Nuclear Physics Division Data Acquisition Group

# **Description and Technical Information for Version 4 Trigger Supervisor (TS) Module**

J. William Gu

Updated on: Dec. 3, 2013

# **Table of Contents**

| Section    | Title                              | Page |

|------------|------------------------------------|------|

| 1          | Introduction                       | 3    |

| 2          | Purpose of TS Module               | 4    |

| 3          | Function Description               | 5    |

| 4          | Specifications                     | 11   |

| 5          | TS operation                       | 14   |

| 6          | Programming Requirements           | 15   |

| 7          | Front Panel and Backplane Pin outs | 48   |

| 8          | Citation                           | 55   |

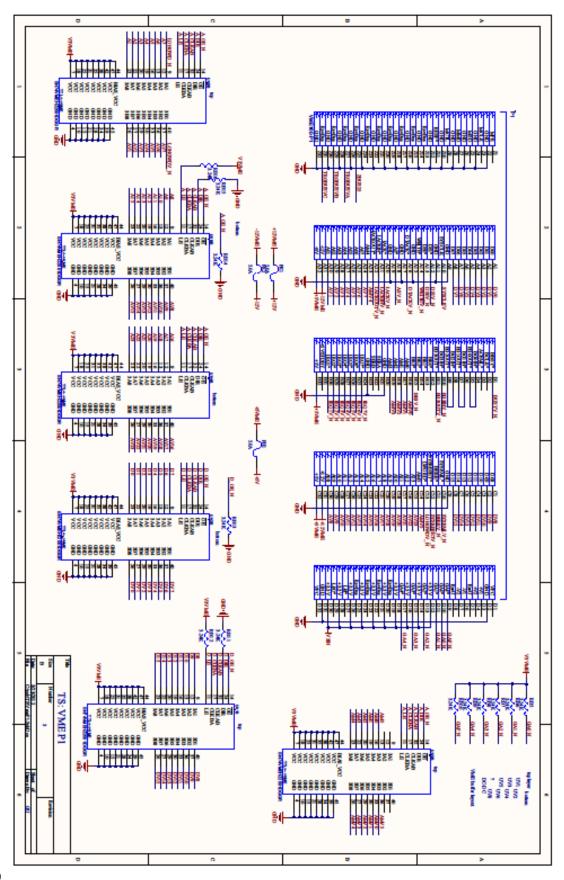

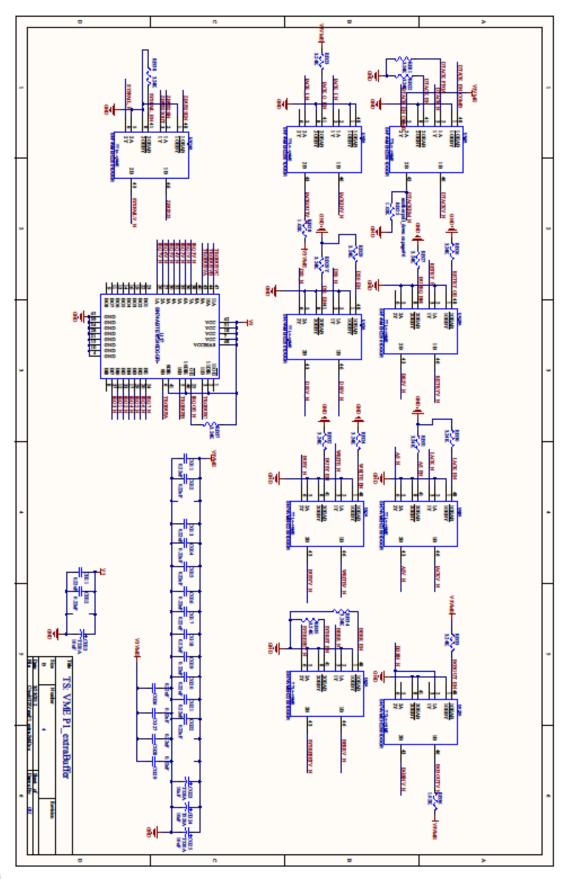

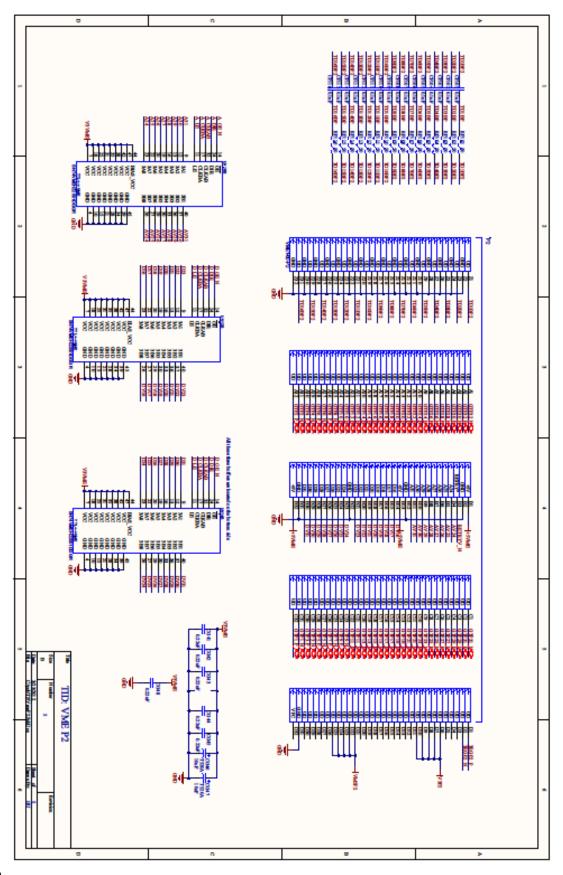

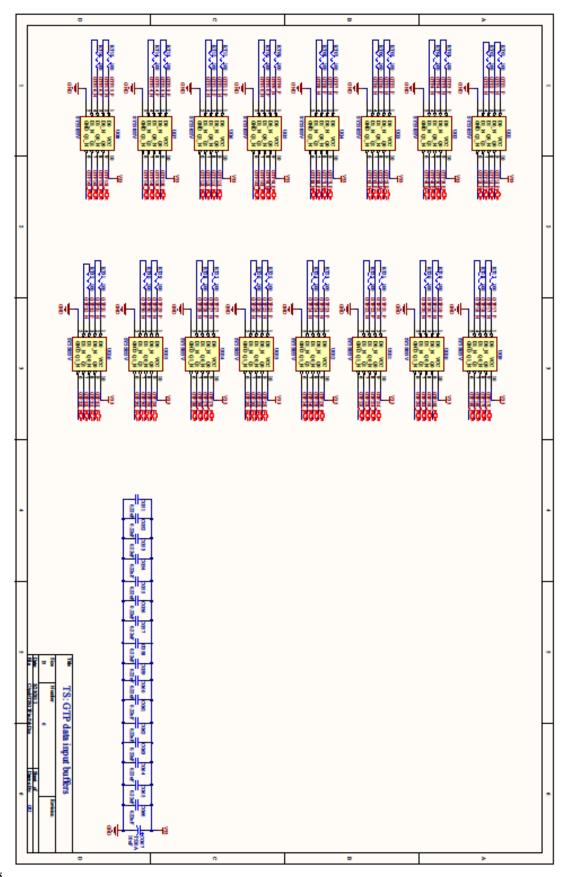

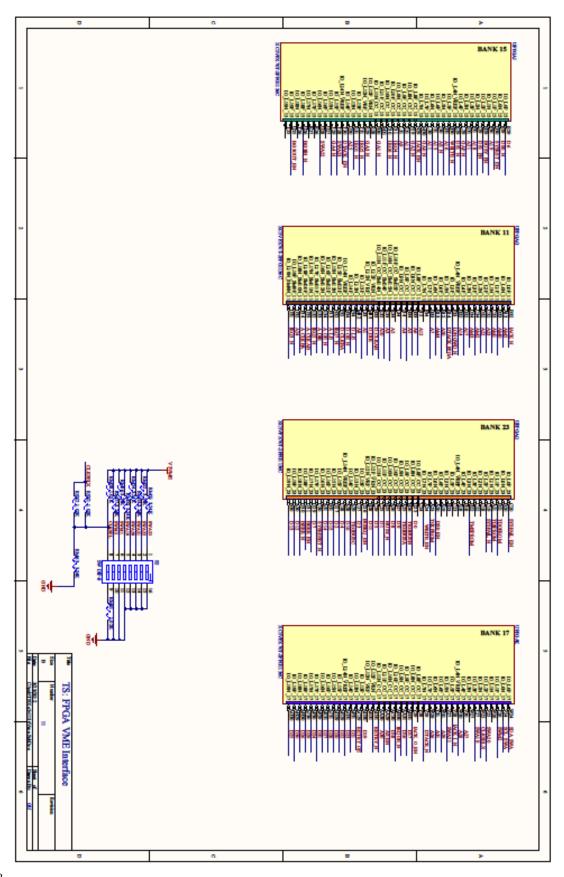

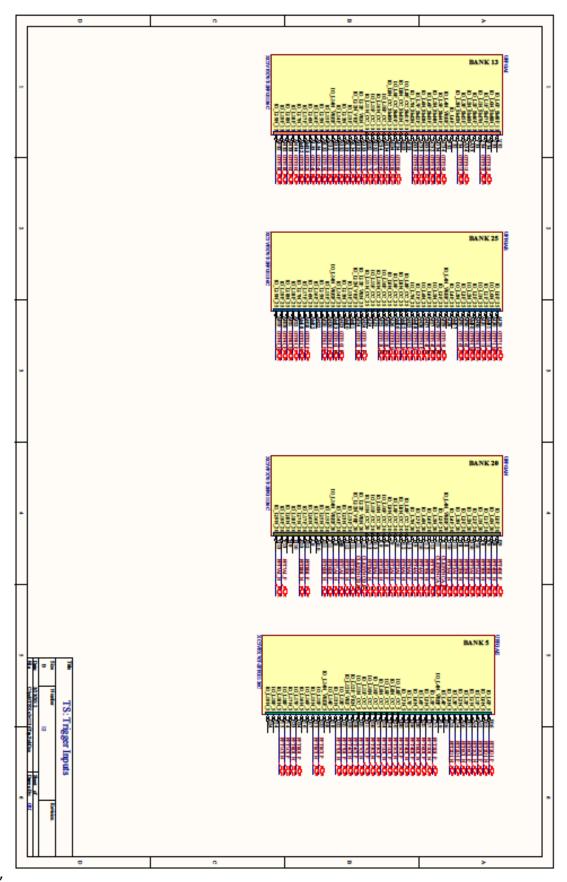

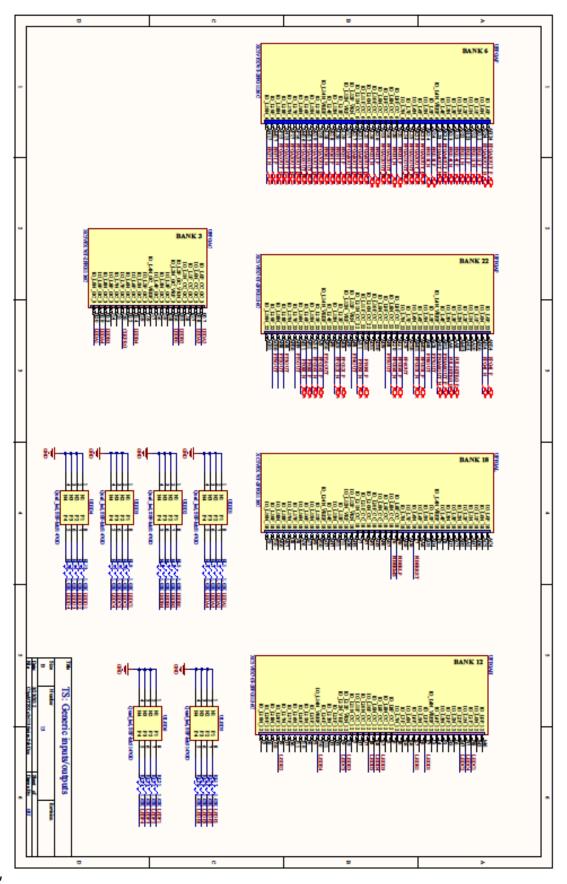

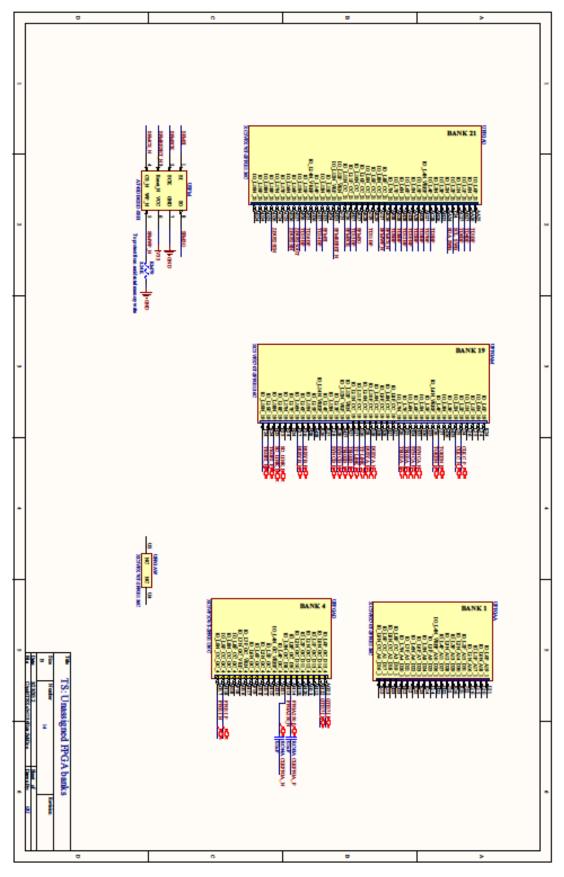

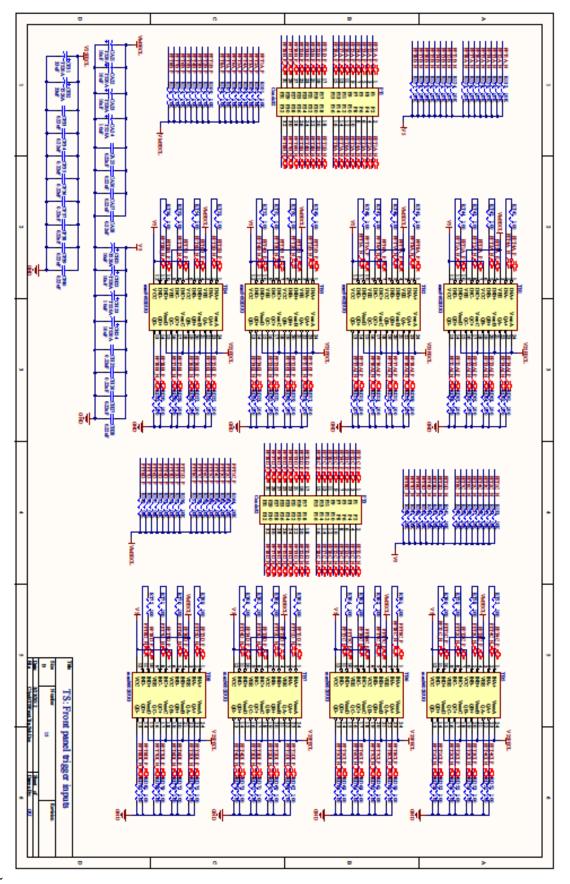

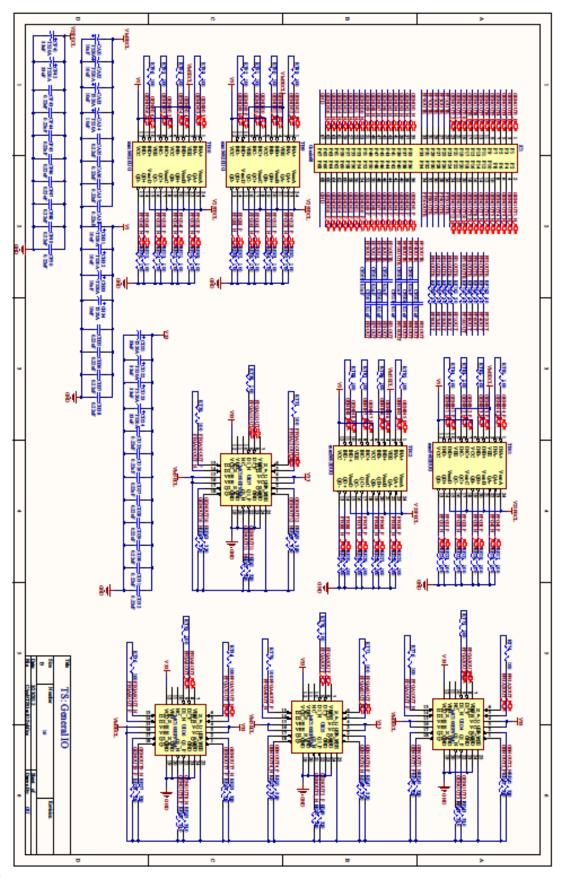

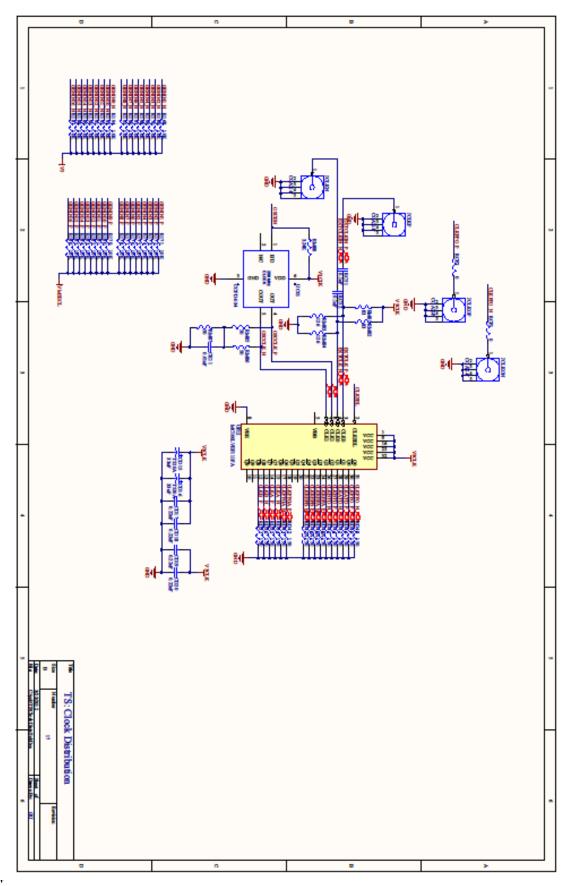

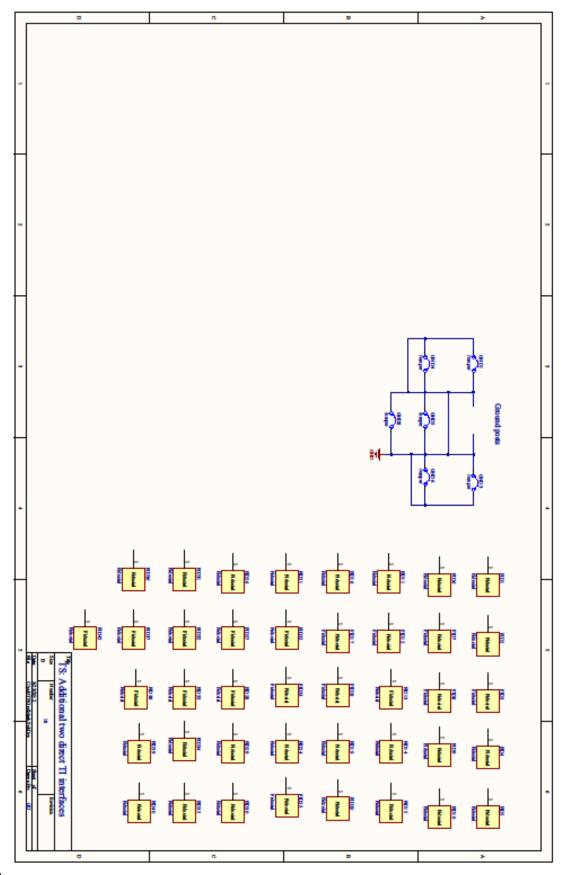

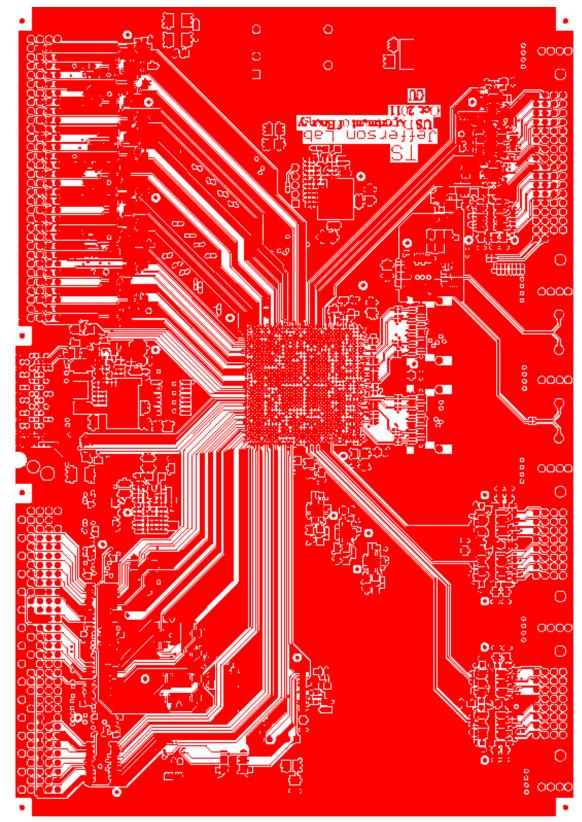

| Appendix A | TS Schematics                      | 56   |

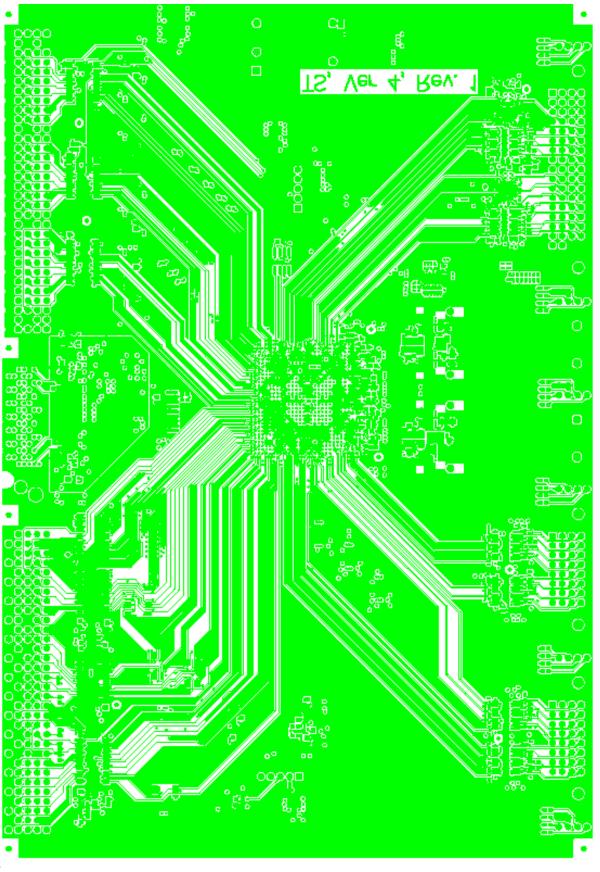

| Appendix B | Fabrication Drawing                | 73   |

| Appendix C | Bill of Materials                  | 75   |

| Appendix D | Data format                        | 77   |

| Appendix E | Revision History                   | 80   |

# **1** Introduction

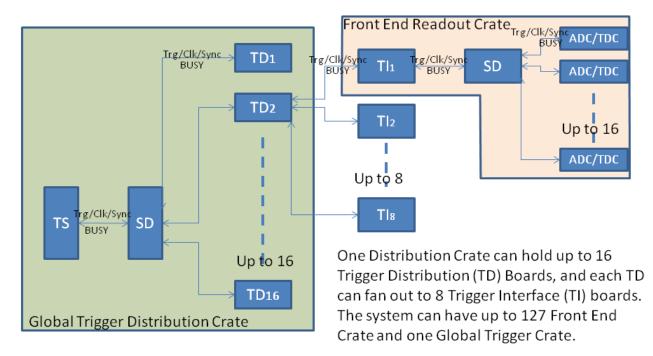

The Trigger Supervisor (TS) version 4 module is being designed for the Jefferson Lab 12GeV upgrade, mainly for Hall-D [ (Collaboration G. , 2009)] and Hall-B [ (Collaboration C. , 2009)], with other experimental Halls [ (experiments, 1990)] compatibility. This module is the interface between the trigger system and data acquisition system of the experiment. The TS acts as the central control point for data acquisition. It provides a synchronous clock source to the experiment, trigger signal for the data readout, and a sync signal to align the frontend electronics. Together with the Trigger Interface (TI) boards, Trigger Distribution (TD) boards and Signal Distribution (SD) boards, the clock, trigger and sync signals are distributed to the frontend electronics, and the BUSY signals from the frontend electronics are monitored. Figure 1 shows the placement of the TS, TI, TD and SD in the global trigger distribution scheme in experiment setup.

#### Figure 1 Trigger distribution scheme

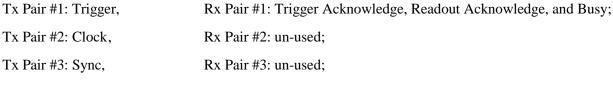

There is one TS module in the system. The TS receives the trigger from GTP (in global trigger crate) through four copper cables via the VME P2 backplane and a P2 data transition card. The TS sends event readout signal through the distribution system. Depending on the frontend DAQ status, not all the triggers will generate event readout signals. Normally, the TS board is located in the last payload slot (Payload slot#18) in the trigger distribution crate. The trigger/clock/sync signals from TS pass to the Signal Distribution (SD) module in switch slot #B. The SD will fan out the signals to (up to) sixteen Trigger Distribution (TD) modules located in the payload slot #1-16. Each TD can fan out to (up to) eight Trigger Interface (TI) modules in frontend crates. The trigger distribution system can have up to 127 frontend crates, the global trigger crate, and the global distribution crate. The busy signals from frontend electronics can propagate back to the TS in the other direction. Figure 2 shows the crate level diagram.

Within the crate, the signals are mainly transmitted via the VXS P0 connector. Optic fibers are used for transmission between crates, that is, between TI and TD modules. The quad optic transceiver AVAGO HFBR-7924 is used with multiple-fibres cable. The four optical Tx/Rx pairs (between TI and TD) are assigned as following:

Tx Pair #4: loop back,

Rx Pair #4: fiber latency measurement.

Figure 2, Trigger distribution at crate level diagram

# 2 Purpose of the module

The TS is the top level control module for Data acquisition system. It receives trigger from trigger system. It generates readout trigger (events) from the input trigger signals. The inputs to the TS are triggers, and the outputs from the TS are events.

The TS in the global trigger distribution crate receives 30 level one trigger primitive signals and two source synchronizing clocks from the Global Trigger Processor (GTP) via four copper cables through a VME P2 transition card. The TS receives another 30 trigger signals and two source synchronizing clock signals through two 3M CONDO front panel connectors. TS also receives another 15 asynchronous trigger signals through another front panel connector. The TS can pre-scale the primitive trigger signals, and generate final event trigger

signals to initiate data acquisition process, taking into account of the front-end electronics status (BUSY for example).

In addition to the trigger generation from GTP and front panel, the TS can also accept calibration triggers by VME command, random triggers, and predetermined number of triggers by VME. The TS supports more than 256 different event types (8 bits). The 8-bit trigger type, together with another three-bit trigger source, will be sent to the front end Trigger Interface (TI) via SD/TD modules. If the front-end electronics buffer is (almost) full (defined as BUSY), or the trigger generation is inhibited, the TS will not generate event readout signals to initiate further data readout, instead, it will start a dead time counter as data acquisition efficiency. The trigger word (16-bit word) will be serialized by the derived 62.5 MHz (250 MHz divided by four) clock.

The TS will supply the experiment with a synchronous 250 MHz clock as system clock, which is sourced either by an on-board oscillator or by an external input through the front panel. The external input could be the synchronous 250 MHz clock from the accelerator. If the accelerator synchronized clock is used, the detector timing measurement (Time of Flight for example) could be easier.

The TS will generate a SYNC signal to align the trigger signals received by the TI boards through their deserializers. The details of the SYNC can be found in the trigger distribution documentation. Using the SYNC signal, and the fiber length measurement, the event readout trigger signals can be aligned to within 4 ns across all the Trigger Interface (TI) boards (or front end crates).

Another purpose of the TS is to control the data acquisition. If the data acquisition cannot keep up with the readout trigger, the data buffer on frontend electronics may overflow. The front end can assert a BUSY signal, and the BUSY will propagate to the TS. The TS can make decision to limit the trigger rate (for data readout), or even stop the trigger completely. If the trigger is inhibited (by asserting the inhibit signal from front panel), the TS will block all the triggers for data acquisition.

There are two optional optic links, which use the same front panel space as clock input and clock output. With these two links, the TS can directly connect to the Trigger Interface board (without SD board and TD board). This is especially useful when integrating with Global Trigger Processor and testing the trigger system. The TS will behave like a "mini" trigger distribution crate. The TS can also drive the P0 connector in pulse mode, so that the TS board behaves like a TI board driving one data acquisition frontend crate.

# **3** Functional Descriptions

#### 3.1 General description

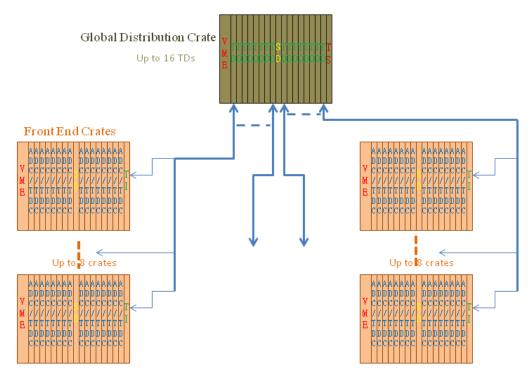

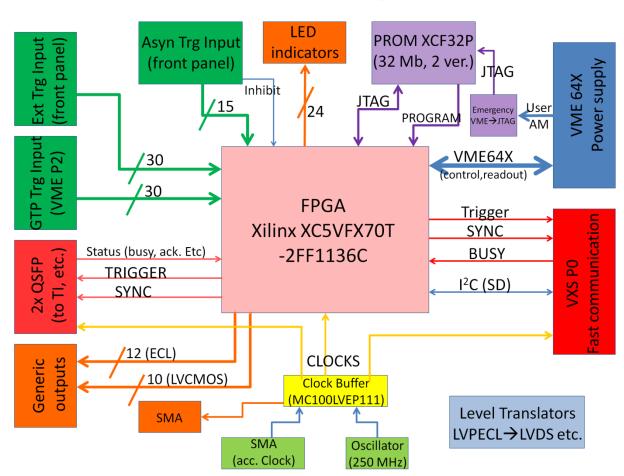

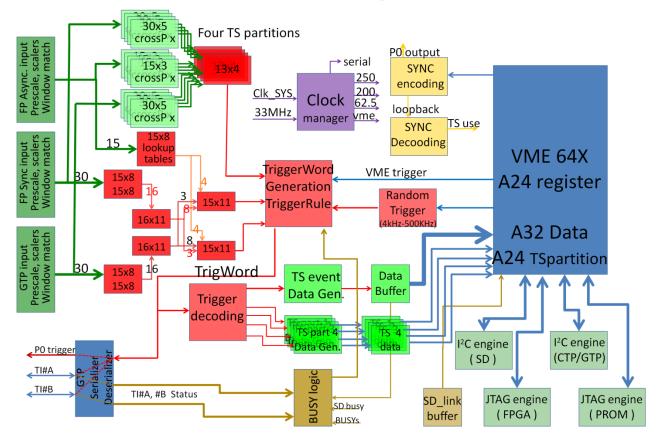

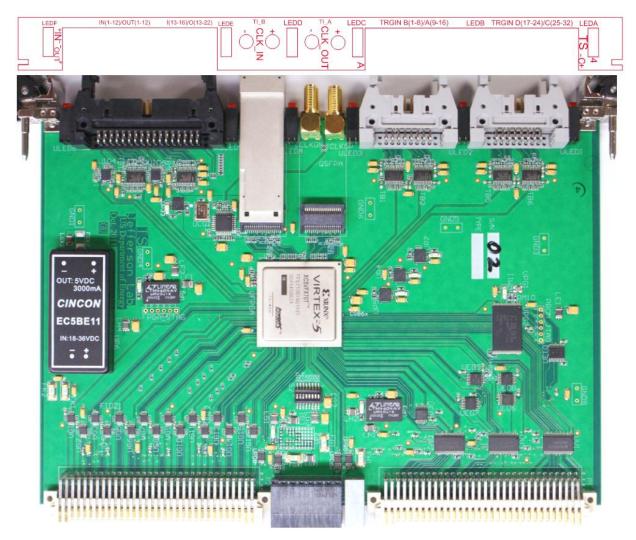

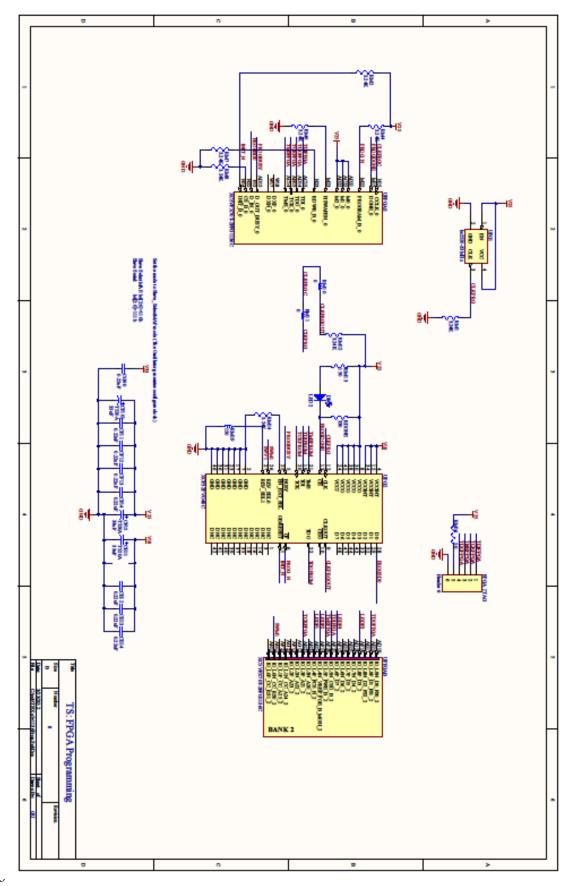

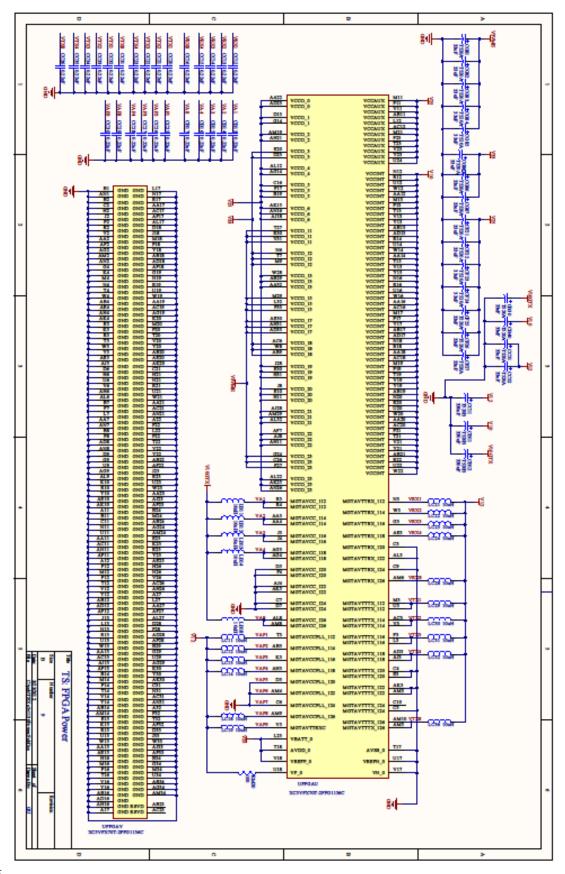

Figure 3 shows the block diagram of the TS module, indicating the major components used in the design. A Xilinx XC5VFX70T-FG1136 FPGA is used to generate the data readout trigger (from three sources). It also interfaces with VME, serializes the trigger words at 16ns intervals, and distributes to the frontend electronics. It generates the SYNC signals to align the whole experiment. The FPGA may also limit or disable the trigger depending on the front-end status. The clock is distributed by the MC100LVEP111, a multiplexer and fan out clock driver component. The simple fan-out structure will not introduce unnecessary jitter on the clock.

Figure 3 Trigger Supervisor (TS) functional diagram

# TS board block diagram

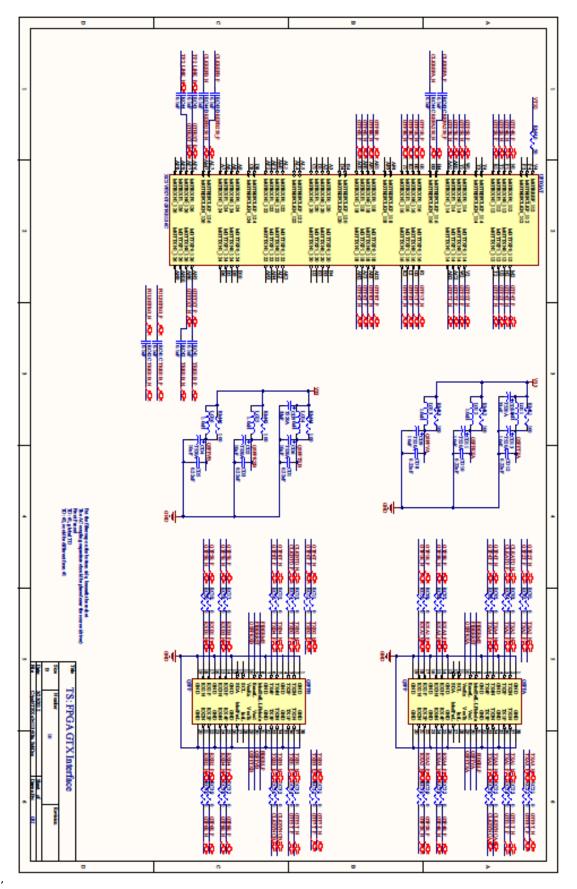

# 3.2 Fiber links

The AFBR-79Q4Z is a multi-channel (4 Rx, 4 Tx) fiber optic link. It is technologically more advanced than HFBR-7924, and it is cheaper too, as it is widely used in Infiniband applications. For the TS, two modules are put on the front panel. The two QSFP modules give the TS extra flexibility, that is, it can bypass the SD-TD fan outs, and distribute triggers directly to two TI modules in the frontend crates. The TS will serve as a "mini" trigger distribution crate with full Global Trigger Processor (GTP) board inputs. If this feature is not necessary, the two QSFP modules are connected to FPGA MGT transceivers, each can be a four channel full duplex transceivers for data transfer testing. With the potential of MGT, the total data rate can be more than 40 Gbps. (The XC5VFX70T MGT limit is 6 Gbps per channel)

The AFBR-79Q4Z will have Trigger, Clock, Sync as Tx channels, trigger acknowledge and BUSY as Rx channel. Another generic Rx/Tx pair for future expansion (as the extra Xilinx MGT modules in the FPGA allows), or four channel full duplex transceivers for future development.

# 3.3: Clock generation:

One of the TS's major functions is the pipeline clock generation. The clock is generated by its on-board low jitter oscillator (Crystek CCPD-034M-50-250, 250 MHz). The TS can also accept an external clock input through front panel. The external clock input can also give the flexibility of using the accelerator synced clock if we can get one and we need to.

The TS uses a MC100LVEP111 to distribute clocks to the FPGA, two optical links, and SD through P0 connector. The FPGA will generate other frequencies as needed from the 250 MHz clock.

# 3.4 Readout triggers generation (Event type generation):

The readout trigger generation is the most important function for the TS. The Data Acquisition system treats each trigger as one event, and the pipeline frontend data are grouped by events, or triggers. The trigger system (electronics) generates the level one trigger primitives. The TS matches the level one trigger with the DAQ events. The TS should maximize the DAQ efficiency without messing up the events.

The trigger input signals can be stretched in time to cover the full event. Because of the trigger primitive natural latency uncertainties (detector signal flight time etc.), this signal extension will match the event to the real beam collision. An extra inhibit window can also be set to veto the next event, so no two events will be generated from the same collision. These two parameters can be adjusted independently in ranges from 8ns to 500ns.

The earliest level one trigger primitive timing will be used to tag as the event timing. The tag precision is 4ns. This timing information will be sent as part of the trigger word to the TI, so the TI can generate trigger (decode trigger) in 4ns precision, although the trigger word is transferred every 16ns (on 62.5 MHz clock).

<sup>\*</sup>This option (8/3 split) is good for more independent GTP or Ext trigger

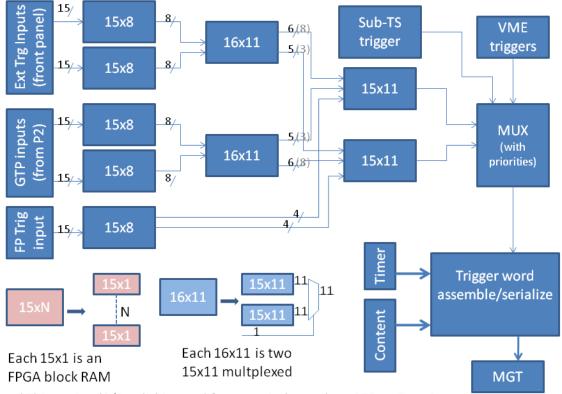

Figure 4 Trigger (event) generation in TS

The level one trigger primitives (GTP inputs or external inputs) can be stretched in time and pre-scaled before being used to form a readout trigger type. The trigger type is a look up table with 75 address inputs and two 11 bits event type outputs. This is implemented using the block RAM in the FPGA. The lookup table is implemented physically by 106 36Kbit blockRAM modules inside the Xilinx FPGA. The lookup table can be reloaded every time the power is up, or the trigger pattern needs be changed. In standard VME A24D32 access, the block RAM loading takes less than one second. It is possible to reload the lookup tables by an external non-volatile flash memory. The TS can be reconfigured without re-compiling the FPGA.

The detailed GTP trigger primitive inputs and their lookup table structure is shown in figure 4. An asymmetric event type definition is used, which is described in details in section 3.8.

The readout trigger collisions happen when two or more event readout triggers are needed to send in the same time window (16 ns), or the front end electronics is busy, or the trigger is inhibited. If the trigger collision happens, the trigger will be lost. The trigger collision condition is sent out. The TS will record it as busy time. Together with the live time, the TS is recording the trigger efficiency, or data acquisition efficiency. When a higher priority trigger is generated and the lower priority trigger is lost, there is no dead time introduced.

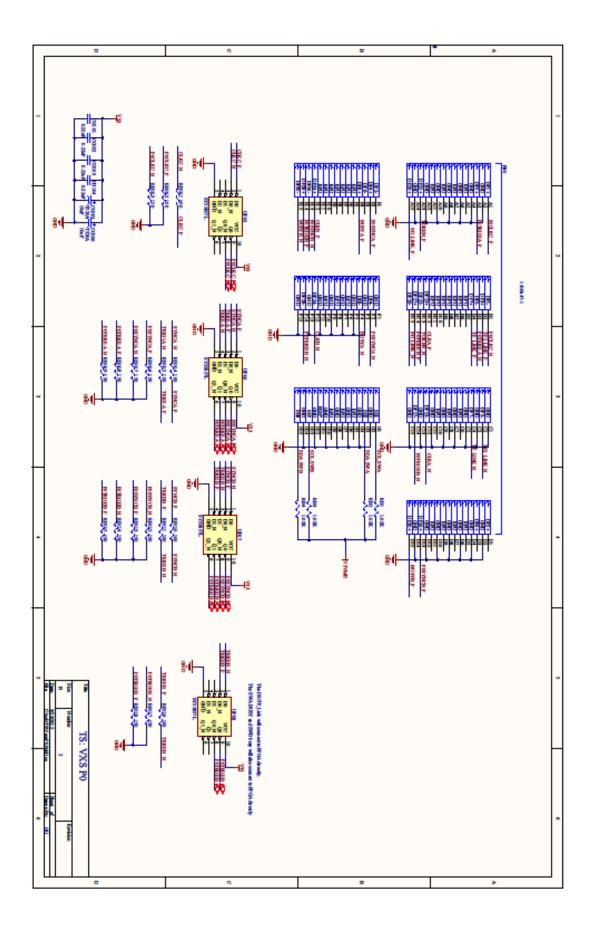

# 3.5: TS partitions (Sub-TS)

To facilitate the detector commissioning and sub-detector tests, the TS can also generate triggers as four mini trigger supervisor boards (Sub-TS). The sub-TS works in parallel with the main TS functions. Each sub-TS has its own event type look up table and data stream.

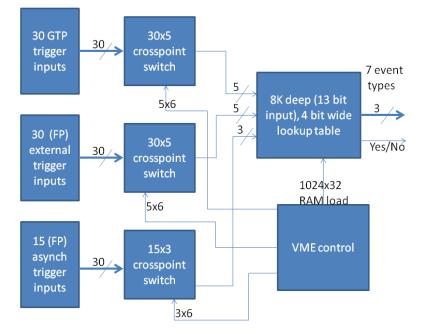

Each sub-TS can have up to 13 level-one trigger inputs. These 13 trigger inputs can generate up to 7 different event types by a lookup table implemented by the FPGA block RAM. The user can choose any five inputs from the 30 GTP level one triggers, any five from the 30 front panel synchronous inputs (external trigger), and any three from the 15 front panel asynchronous trigger inputs. The seven event type is encoded in three bits (code 0 is excluded). Figure 5 shows the diagram of one sub-TS event type generation.

Figure 5 sub-TS event type generation 9

The four sub-TS work in parallel. Trigger word with bits (15:12) = "1011" indicates that the trigger word is a sub-TS trigger strobe. The detailed trigger word is in section 3.8. Each sub-TS event type uses three bits of the lower 12-bit of the sub-TS trigger strobe word. There is no sub-TS trigger timing information, nor trigger content word. The sub-TS can also work together with the normal TS, though the normal TS trigger strobe has higher priority than the sub-TS trigger strobe word.

In this way, the TI can decode both the standard TS trigger strobe word and sub-TS trigger strobe word. The TI needs to know which sub-TS to enable (extra trigger source). Actually, one TI can respond to multiple sub-TS (partition) triggers.

The TS has trigger data for every event, which can be read out by the A32D32 access (and up to 2esst). Each sub-TS has its own event data, which can be read out by VME A24 D32 single word access.

### 3.6: Serial Flash Memory

A 4 Mb (at least) serial flash memory can be used to store the trigger lookup tables. When the TS is powered down, the memory retains the trigger table. When the TS is powered up, the board will automatically load the lookup table back to the FPGA to initialize the block RAM (as the block-ram is much faster than the external flash memory). If the trigger table is going to be changed (for example, different trigger modes), the user need load the new trigger table into the flash memory, then send a VME command to load the block-ram by the flash memory. In this case, the TS is still operating in the previous trigger mode while the new trigger mode (lookup table) is being loaded. The lookup table needs less than one second to load through VME (A24D32), there is really little point to use this serial flash memory. (The Serial flash memory read needs 1 second if the clock is 4 MHz). Although the serial flash memory is populated on the TS, but the firmware has not been implemented to use it yet.

#### 3.7: Fixed Latency CLKSYNC

The CLKSYNC signal is a 250 Mbps serial line that operates in synchronous mode. This serial link allows a 4-bit command to be sent at chosen 4 ns points in time. CLKSYNC is synchronized to the master clock CLK250 and is sampled every 4ns. The line is considered to be idle when more than 4 samples in a row are read '1'. A command is sent between idle times by sending first a '0' followed by the 4-bit command, LSB first. After the command has been sent, a final '1' is sent so that the line will return to the IDLE state. The encoding portion of this serial protocol is performed on the TS in the FPGA. The CLKSYNC output from the FPGA can be delayed (time adjustment) in the precision of 80 ps by the FPGA IODELAY. As the clocks are synchronized and sourced by the TS, this delay setting is not expected to change between different firmware versions. The TS will send the CLKSYNC to the TD boards via P0 and SD. The TD will fan out to the TI boards via optical transceivers. The CLKSYNC is Manchester encoded to balance the differential lines.

The CLKSYNC is synchronized across the TI boards by applying different delays on the TI boards. The delays are determined by the fiber latency measurement. The CLKSYNC link is used in conjunction with a synchronous FIFO to enforce a fixed latency on the serial trigger link. On the TI board, the trigger word is clocked into a FIFO using the FPGA built in MGT transceivers and clocked out of the FIFO using a 62.5MHz clock derived from (and in phase with) the 250 MHz system clock. At startup the FIFO is reset (0 words) and reading the FIFO is disabled. No words are written into the FIFO since the TS is not yet transmitting data words on the trigger link (i.e. received data valid signal is not asserted). Acceptance of triggers by the TS is also

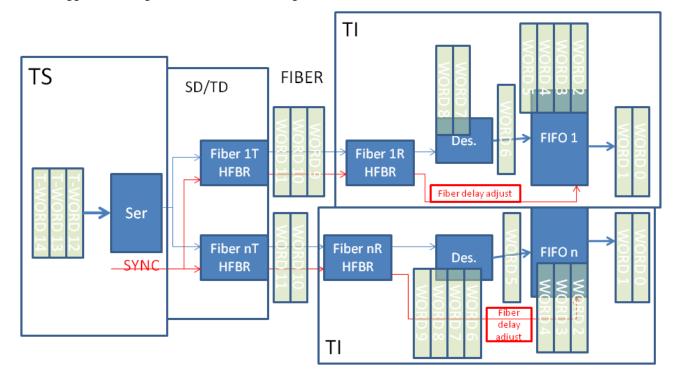

disabled. The serial trigger link is idle words only. On trigger start, the TS starts transmission (trigger words and/or timing words) on the trigger link. The TI will write the deserialized data (valid data, that is non-idle data word) to the FIFO. After some delay (VME register controlled) from the trigger start, the TS issues a TRG\_START command on the CLKSYNC line. When TI receives the TRG\_START from CLKSYNC line, the TI resets the trigger FIFO readout address, and enables continuous readout of the FIFO. As the CLKSYNC lines are fiber length adjusted and the 62.5MHz clocks are phase aligned, the trigger words from the TI board FIFO are synchronized across the system. In TS and TI MGT transceivers, the phase alignment is used to remove the elastic buffer delays as the Tx/Rx modules are using the same clock (or the clocks generated from the same clock). The trigger word alignment is illustrated in figure 6:

Figure 6 Illustration of the Global Trigger Synchronization process

The CLKSYNC link is also used to synchronize the lower frequency clocks derived in the TI from the distributed system clock (CLK250). At startup, the TS issues a CLKSYNC command CLKRESET, which is phase aligned with the 62.5MHz clock on TS. The CLKRESET resets the clock distribution chip (AD9510) on the same CLK250 edge, assuring that the lower frequency clocks (125 MHz, 62.5 MHz, 41.67 MHz and 31.25 MHz) are in phase across all the TI boards, and in phase with the 62.5 MHz clock on the TS board. This command is sent before the TI sync command. The delay between them is determined by the maximum MGT module reset recovery time, as the MGT clock is changed (AD9510 clock reset). The time could be several milliseconds.

#### 3.8: Encoded Trigger Word

A 1.25Gbps serial link operating over the fiber is used to distribute the 16bit trigger word every 16ns. There is also a link going in the opposite direction, allowing status words to be sent back to the global trigger distribution crate. The 16bit trigger words are decoded as follows (TS->TD->TI flow):

Trigger strobe word – generated by the TS in response to the acceptance of a level 1 trigger as a DAQ event. Upon receipt, the TS encodes this word with highest priority. The TS transmits this word with fixed latency relative to the accepted trigger. Two-bit timing information is added in the word to distinguish which quadrant of the 16 ns period the trigger is generated, so it is fully compatible with the 4ns pipeline design architecture. The TI distributes trigger signal in 4ns precision.

Trigger content word – additional information about this trigger event for use by the ROCs. It is queued in a FIFO and sent in any frame not used by a trigger strobe word. The TI matches the trigger strobe and trigger content words by the order of their reception. The Trigger content words could include an event counter. The TI can use this content word to check its synchronization if any trigger is missing by the TI/TD. The TI will send trigger acknowledge back to the TD for missed trigger check, so this check seems redundant. Right now, the trigger content word has not been used yet.

Control Word – some commands. They can be queued in a FIFO and sent in any frame not used by a trigger strobe word. Right now, this is connected to a VME register directly. The decoding is depending on the TI. In current firmware, the control word can be used to generate a single VME trigger.

Master Time Word – since the link must always be transmitting valid data (non-idle data) to keep its latency fixed, bits [13:2] of the TS time is transmitted whenever no other word types are available. Bit(1:0) is transmitted in trigger strobe words. By continuously receiving bits [13:2] of the TS time, each TI can promptly detect if its subsystem has lost global synchronization (i.e. compare the global time with its own time). Otherwise, the loss of synchronization could only be detected at the event building stage. The continuous transmission of 'known' (i.e. predictable) data also allows one to monitor the integrity of the link. The necessity to implement the checking depends on the reliability of the link.

| Bit15 | Bit14 | Bit13 | Bit12 | Meaning of    | Word Type       |                |                  |  |  |

|-------|-------|-------|-------|---------------|-----------------|----------------|------------------|--|--|

| 0     | 1     | 0     | 0     | Lower 12 bi   | Time            |                |                  |  |  |

| 0     | 1     | 0     | 1     | Control or C  | Control         |                |                  |  |  |

| 0     | 1     | 1     | 0     | TI legacy tri | (TS) VME        |                |                  |  |  |

|       |       |       |       | Tquad(1:0)    | trigger type    | (Trg2, Trg1) E | Trigger Strobe   |  |  |

|       |       |       |       |               |                 |                |                  |  |  |

|       |       |       |       |               |                 |                |                  |  |  |

| 0     | 1     | 1     | 1     | Additional T  | Trigger Content |                |                  |  |  |

| 1     | 0     | 0     | 1     | Tquad(1:0)    | Trigger type    | A, (GTP maj    | Trigger Strobe A |  |  |

| 1     | 0     | 1     | 0     | Tquad(1:0)    | Trigger Type    | e B, (EXT ma   | Trigger Strobe B |  |  |

| 1     | 0     | 1     | 1     | subTS#4       | subTS#3         | subTS#2        | subTS#1          |  |  |

This table shows the format of the trigger word

Trigger Type A (or Trigger Type B): Bit(9:8):

00: not defined yet

01: Trigger1 will be generated by TI;

10: trigger2 will be generated by TI;

11: Sync\_event, and trigger1 will be generated by TI too. either periodic sync event or forced sync event

# The trigger format can be easily changed as long as the TS encoding and TI decoding are consistent.

### 3.9 VME interface

The TS is a VXS payload board. It is compatible with VME64x backplane. Normally, it is a VME slave board, with interrupt capability. The TS is implemented the same way as the TI/TD board.

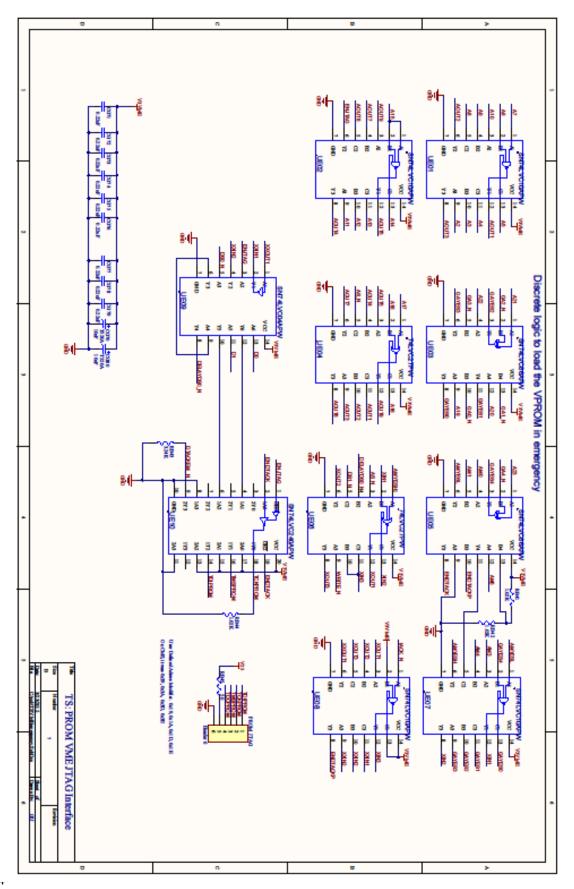

For simplicity, three kinds of VME address modifier codes are implemented. (1), User defined address modifier. This is similar to the A24 address modifier. It is used to load the PROM by the on-board discrete components. (2), Standard A24 address modifier. This is used for registers read/write on the FPGA, slow controls of the TS peripherals, and Sub-TS data readout. (3), A32 data transfer. This is used to transfer data to the ROC (Read Out Controller). For the details of A32 mode support, refer to the VME interface design (Ed, 2010).

#### 3.10 The Xilinx PROM programming.

The Xilinx XCF32P PROM is used to program the FPGA. It can save one version of the (XC5VFX70T) FPGA firmware when it is used in non-compression mode. It can save two versions of the firmware when bit stream compression is used. It can even save four versions of the firmware when bit stream compression is used and the FPGA resource usage is not too high. The PROM is programmed using VME with emergency logic decoding (that is: discrete logic VME to JTAG engine). It can be addressed in the VME64x crates by its geographical address. If it is in the crate without geographical address, only one TS or one TD in the crate should be addressed as geographical slot#0. To avoid conflict with other VME addressing, the user-defined address modifiers are used for the PROM loading. The emergency logic supports A24D32 user defined address modifier codes: 0x19, 0x1A, 0x1D and 0x1E (Similar to 0x39, 0x3A, 0x3D and 0x3E). Out of the data, bit[1] is used for TDI, bit[0] is used for TMS, and all the other 30 bits are unused. This approach is fully tested on TI/TD boards. This emergency loading provides VME remote firmware loading (and re-loading) even if the FPGA is not working. One 33 MHz on-board oscillator is used to program the FPGA, and used by the FPGA for slow control. The PROM needs be in master mode if bit compression is used.

The PROM can also be programmed by the on-board JTAG connector and VME-JTAG engine (after the FPGA is programmed and working) implemented in the FPGA. The JTAG engine in the FPGA provides VME remote firmware loading with more efficient VME data transfer, but the FPGA has to be working.

#### 3.11: Serial data communication with SD and other switch slot modules

As there is no VME access to the switch slots (SD for example), the TS has implemented an  $I^2C$  bus to each switch slot. The TS will act as  $I^2C$  master, and the switch slot module acts as slave. The  $I^2C$  works in FAST mode with higher clock frequency. For details, refer to the VME to I2C implementation [ (GU, 2010)] documented earlier.

The TS can communicate with the switch slot module via a 250Mbps link, (it is possible to increase it to 500 Mbps using DDR techniques). This is implemented using the Xilinx SelectIO standard differential IO pin pair. The switch slot module can also send data to TS using this link. The direction of the data link depends on the firmware (TS and SD) implementation. This can serve as a complimentary to the slow I2C interface as one

possible usage. Right now, this is implemented as SD to TS one way data transfer. Using this link, the SD can update a block memory on TS directly. [ (GU, 2013)]

### 3.12: Trigger data receivers

The Texas Instruments SN65lvdt100 (Micrel SY55855 on TS prototype boards) LVDS receiver is used to receive the GTP data from P2 backplane. The receiver output (LVDS) goes directly to the FPGA for processing.

The Maxim max9602 differential discriminator chip is used to receive the trigger input from the front panel (external trigger in or generic trigger input). The max9602 uses -5 as VEE, +5 as VCC, and +2.5V as VOUT. It can receive any differential input with common voltage of -2V to +3V (which includes ECL, LVDS, LVPECL ...), and the LVPECL25 output is compatible with the extended LVDS input of the FPGA.

#### 3.13: Readout Synchronization

In addition to the event number and trigger time stamp, the readout can be forced to get synchronized by synchronization events (SyncEvent). There are three ways to generate the SyncEvent.

First, the SyncEvent can be generated periodically by TS (or TImaster). The last event of the every N blocks is generated as the SyncEvent. (for now, the block level, or number of event per block, is up to 255) The N is any value between 1 and 65535, which is set and enabled by A24 register offset 0xD4. When the periodic SyncEvent is marked, the original event type is kept.

Second, the SyncEvent can be forced by VME command to the TS (or TImaster). This event may be any event in the trigger block. It is an added event with event type "00000000". The forced SyncEvent can be generated by VME A24 register offset 0x100, bit#20.

Third, the SyncEvent can also be generated by a front panel signal input.

The TS (or TImaster) will assert a short BUSY (3us) after generating the SyncEvent, and stop further triggers. After receiving the SyncEvent, the TI will generate BUSY, and set the SyncEvent marker in the ROC polling register A24 offset 0x34. The BUSY of TI will propagate to the TS through fibers and P0 backplane. The latency of this should be less than 3us, so that it will overlap with the short BUSY on TS. After the front end data is cleared, and the Readout acknowledge will clear the BUSY on the TI. In pipeline readout mode, If there are more than one trigger blocks to be read out, the very last acknowledgement clears the SyncEvent BUSY on the TI. After all the TI boards clear their BUSY, the TS will distribute trigger again. Depending on the data acquisition mode and the amount of data backed up on the frontend, this process may take tens of microseconds to many milliseconds.

Upon SyncEvent, the trigger distribution will be paused. Users can change the DAQ settings during this time. If no reset in this time period, the event number and trigger time will be continued.

Figure 7 is the function diagram of the TS FPGA, which includes the detailed diagrams in this section (like, figure 4, 5, etc.)

# TS FPGA Block diagram

Figure 7 FPGA function diagram

# 4. Specification Sheet

# 4.1 Mechanical

Single-width VITA 41 Payload Module with the size of 6Ux160mm. It will be positioned in the PP18 of global clock/trigger distribution crate. If there is no SD in the crate, the TS can be plugged in any of the payload slots to act as a "mini" trigger distribution crate.

# 4.2 High speed serial P0 inputs:

BUSY LVDS signals on P0;

I<sup>2</sup>C to VXS Switch slot# B, switch slot #A;

High speed LVDS data link (can be output too).

# 4.3 High speed serial P0 outputs (LVPECL):

Two 250 MHz clock to Switch slot #B; one to the switch slot #A;

1.25 Gbps Encoded (serialized) TRIGGER Signal, or pulsed Trigger1 and Trigger2;

250 Mbps Manchester encoded SYNC Signal;

Pulsed trigger, which used the Trigger2 line on SD to distribute trigger to TD boards.

# 4.4 High speed P2 GTP level one trigger primitive inputs:

250 Mbps GTP trigger primitive inputs via a backplane transition board;

P2 Row A and Row C are used, 32-pairs for 32 GTP inputs (the 1<sup>st</sup> and 17<sup>th</sup> pairs are used as data source synchronized clock);

LVPECL Signal;

Some of the 32-pairs may not be used.

# 4.5 External trigger inputs:

30-bit differential external trigger in four groups with 7/8 bits per group;

Two source synced clocks

# 4.6 Front panel general inputs:

16-bit general purpose differential inputs, which could be additional 15-bit asynchronous trigger inputs and one trigger inhibit (or busy) bit on the 34-pin connector;

250MHz Clock Input (SMA), LVPECL input;

4.7 Front panel general outputs:

10 LVCMOS single-ended outputs (TS status);

12 ECL differential outputs (TS status);

250 MHz clock output (SMA) LVPECL.

4.8 Fiber channel signals: two AFBR-79Q4Z modules (They share the same front panel space as the clock input/output SMA connectors)

CLKSYNC Fixed Latency Link

250Mbps Serial Communication

Manchester Encoded

CLKSYNC to CLK skew variation < 1ns

This link can optionally been connected to the FPGA's MGT Rx/Tx directly;

TRIGGER\_TX/STATUS\_RX

1.25Gbps Trigger Word Line

Provides 16bit parallel data every 16ns

A BUSY status word in the opposite direction, which also includes trigger acknowledge, and frontend data readout acknowledge.

This link is connected to the FPGA's MGT Rx/Tx directly;

#### CLK

250MHz low jitter clock

This link can optionally been connected to the FPGA's MGT Rx/Tx directly;

### SPARE

Generic Rx/Tx pair connected to the FPGA MGT transceiver with loopback capability.

# 4.9 Indicators: Front Panel:

Six sets of LEDs on front panel:

Set 1 (LEDA): TS board status

FPGA is ready;

Board OK;

Lengthened trigger active;

Lengthened VME DTACK indicator.

Set 2 (LEDB): External 30-bit trigger input indicator;

Set 3 (LEDC): GTP 30-bit trigger input indicator;

Set 4 (LEDD): AFBR-79Q4 status

Set 5 (LEDE): 10 LVCMOS, 12 ECL outputs status

Set 6 (LEDF): 15-bit asynchronous trigger inputs and inhibit

On board:

Power OK near each regulator or DC-DC converter; (OFF, if power is OK)

FPGA program DONE; (OFF, if the FPGA is programmed)

#### 4.10 Programming:

VME64x, A24/D32, A32/D64 slave

#### 4.11 Firmware loading:

VME to JTAG A24D32 with user defined AM (Address Modifier) for remote firmware loading with redundant On board JTAG connector;

Custom VME to JTAG engine implemented in the FPGA using A24 standard AM.

It is possible that two revisions of the firmware be stored in the PROM simultaneously, with one as backup; or as two different configurations of TS. But as the TS firmware got more complicated, the FPGA resource usage increased to a point that the PROM is no longer large enough to hold two compressed firmware designs.

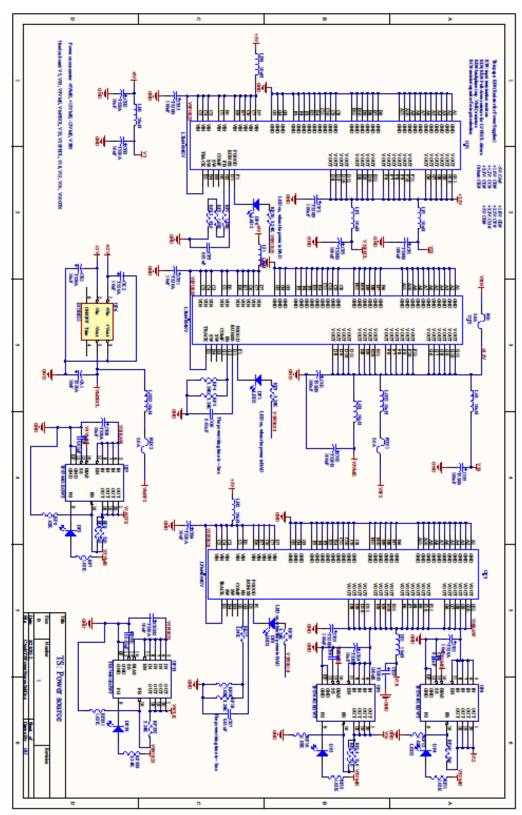

4.12 Power requirements:

+3.3v @ 1.5 Amps; +5V @ 4 Amp; +12V, -12V @ 0.3 Amp (From Backplane), total < 35 W;

DC-DC converters for +1.8V, +2.5V, +3.3V and -5V, and Local regulators for other required voltages: +1.0V, +1.2V, +3.3V clock.

# 4.13 Environment:

Forced air cooling: Weiner standard

Commercial grade components (0-75 Celsius or better)

# **5 TS operation procedure:**

The TS needs be properly set and plugged into the proper crate and slot. Damage may happen to the TS, the crate, or other PCBs in the crate if the right procedure is not followed.

#### 5.1 TS Power supply:

The TS use +3.3V directly from VME64x crate. It can also generate its own +3.3V supply by a DC-DC converter from +5V from VME. This is selected by loading the on-board FUSE and/or DC-DC converter. To avoid conflict, do not populate both (VXS crate is a VME64x compatible backplane).

# 5.2 Hardware setting (Switch etc.):

An 8-bit switch is used to set the TS working mode:

Bit8: LVPECL, open=high, Clock source selection. When high, the clock source is on board oscillator; when low, the clock source is front panel clock input. The switch setting can be overwritten by a software setting (FPGA pin drive).

Bit7: open=high, A24 address space selection. When LOW, use the VME64x GA(4:0); HIGH, use the switch bit(5:1) as A24 address space setting;

Bit6: FPGA firmware revision selection, low: revision 0, high: revision 1; This can be overwritten by the FPGA MULTIBOOT RS0 if the revision 1 should fail (and if rev1 is selected). As the PROM can only save one firmware version, this switch needs be set to LOW.

Bit(5:1): A24 address space A(19:23). As the TS and TD are the only VME custom modules in the global trigger distribution crate, the switch Bit(5:1) and Bit7 will most likely be left unused as both the TS and TD support the Geographic address GA(4:0), and the VXS crate is VME64x compatible.

# 5.3 Software setting:

After the board is properly set, and plugged in the right slot, some software setting needs be applied for the board to work. The TS software setup sequence: (The TS may not work if the sequence is not followed)

- TS clock selection: This is important for the trigger distribution system to work properly

- Trigger table loading: This is the most important step, and it is required every time the TS is powered up, or the FPGA is reprogrammed;

- Some other reset/initialize in specified order. TS initialization is a whole trigger distribution issue (TS/TD/TI), not just TS itself. See the software example for proper order.

# 6. VME Programming Requirements

There are three categories of Address Modifier codes are supported on the TS: the user-defined Address Modifier codes (A24) for emergency firmware loading; Standard A24 for FPGA register read/write and slow control; A32 block transfer for VME data readout. The A24 address space is set by the 5-bit Geographical address of the VME64x backplane or the onboard binary switch (as mentioned in section 5.2).

# 6.1 VME to JTAG emergency loading:

The AM[5:0] user defined codes are used for this logic. This works even before the FPGA is programmed and working. It is almost the same as A24D32 mode. The valid AM codes are: 0x19, 0x1A, 0x1D and 0x1E. These AM codes are user defined, and similar to the AM codes 0x39, 0x3A, 0x3D and 0x3E.

The valid address bits are A[31:24] do not care; A[23:19]=GA[4:0] for VME64x crates, or A[23:19]=0 for non-VME64x crates; A[18:2]=b'00011111111111111.

Data bit[1] is used for TDI; data bit[0] is used for TMS.

For example, if the board is in slot#5 (that is  $\sim$ GA(4:0)= 11010), you need write to A(23:0)=0x28fffc.

If data(1:0)=00, both TMS and TDI will be low; if data(1:0)=01, TMS is high, TDI is low; if data(1:0)=10, TMS is low, TDI is high; if data(1:0)=11, both TDI and TMS are high.

The normal A24 address should try to avoid this address (0x0fffc).

A more advanced example: Instruction register shift (8-bit, shift in 0x5a) starting from/end up at the 'reset idle' mode: 14 consecutive writes to the address 0x28fffc with AM=0x19, 1a, 1d or 1e, the data are 1, 1, 0, 0, 0, 2, 0, 2, 2, 0, 2, 1, 1, 0 respectively.

| Data | 1  | 1  | 0  | 0  | 0 | 2 | 0 | 2 | 2 | 0 | 2 | 1 | 1  | 0  |

|------|----|----|----|----|---|---|---|---|---|---|---|---|----|----|

| TMS  | Н  | Н  | L  | L  | L | L | L | L | L | L | L | Н | Н  | L  |

| TDI  | 0x | 0x | 0x | 0x | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0x | 0x |

"TMS H" means logic High, "TMS L" means logic Low, "TDI 0" means 0 or Low, "TDI 1" means 1 or High, and "TDI 0x" means DO NOT CARE by the JTAG, but the set value is 0.

# 6.2 Configuration Registers:

A24D32 are used for register read/write. Similar to the emergency loading logic, the base address is determined by the Geographic Address in VME64x crate, and external switch for non-VME64x crate. That is, A[23:19]=GA[4:0], or SW[5:1]. [0xXX, BIT(m,n)] means the register offset and bits in old TI firmware design.

➤ Address offset: 0x00000: Board ID:

Bit 7-0 (R/W): Crate ID; Reset default 0x00; [0x00, BIT(7:0)] Bit 12-8 (R): A24 address, higher 5 bits; Reset default 000 [0x54, BIT(4:0)] Bit 13 (R): '1': TS is in running mode, it is GA parity bit for TI; Bit 15-14 (R): '10': TS is in running mode (no more register changes), others: TS not in running mode; Bit 31-16 (R): hex 0x71D5 (0x71: TI, 0x75: TS, 0x7D: TD, 0x71D5: TIDS). [0x54, BIT(31:16)]

- > Address offset: 0x00004: Optic transceiver enable:

- Bit 7-0 (R/W): on TI: HFBR#8, #7, ... #1 Enable, Reset default 0xFF all enabled. [0x04, BIT(7:0)]

- Bit 0: '1' enable HFBR#1, '0' disable HFBR#1; ('disable' means 'power down')

- Bit 1: '1' enable HFBR#2, '0' disable HFBR#2;

- Bit 2: '1' enable HFBR#3, '0' disable HFBR#3;

- Bit 3: '1' enable HFBR#4, '0' disable HFBR#4;

- Bit 4: '1' enable HFBR#5, '0' disable HFBR#5;

- Bit 5: '1' enable HFBR#6, '0' disable HFBR#6;

- Bit 6: '1' enable HFBR#7, '0' disable HFBR#7;

- Bit 7: '1' enable HFBR#8, '0' disable HFBR#8;

- On TS, they set the mode for TS's two QSFP optic transceiver:

Bit 0: unused

- Bit 1: FiberLP; Low Power select; but not valid for this transceiver (Class 1 power level module, 1.5W)

- Bit 2: FiberMS, low true, module select; this select the module for I2C interface active.

- Bit 3: FiberRst, low true, optic transceiver reset;

- On TSrev2 and production TS, this register is not used

- Fiber Reset is done through offset 0x100, bit 5;

- Fiber module select and monitoring are done through offset 0xD8;

Bit8: Enable the P0 (SW#A, SW#B) trigger and SyncReset signal, default is 1 to enable; When disabled, the Trigger/SyncReset stay LOW.

> Address offset: 0x00008: Interrupt setting:

Bit 7-0 (R/W): Interrupt ID; Reset default 0xC8 [0x08, BIT(7:0)] Bit 10-8 (R/W): Interrupt level; Reset default 5; [0x08, BIT(10:8)] Bit 16 (R/W): IRQ enable. Reset default: 0, used to enable INTERRUPT; [0x04, BIT(13)]

> Address offset: 0x0000C: Trigger delay and Pulse width:

Bit 7-0 (R/W): Trigger\_1 delay, (n+1)\*4 ns; Reset default 0x07; [0x0C, BIT(7:0)] Bit 15-8 (R/W): Trigger\_1 Pulse width (n+1)\*4 ns; Reset default 0x07; [0x0C, BIT(15:8)] Bit 23-16 (R/W): Trigger\_2 delay, (n+1)\*4 ns; Reset default 0x07; [0x0C, BIT(23:16)] Bit 31-24 (R/W): Trigger\_2 Pulse width (n+1)\*4 ns. Reset default 0x07; [0x0C, BIT(27:24)]

Address offset: 0x00010: A32 address space:

Bit 13-5 (R/W): Address Max; Reset default 0x1FF; [0x10, BIT(13:5)] Bit 22:14 (R/W): Address Min; Reset default 0x000; [0x10, BIT(22:14)] Bit 31-23 (R/W): Base Address. Reset default 0x100; [0x10, BIT(31:23)]

Address offset: 0x00014: Block size:

Bit 7-0 (R/W): Block size. Reset default 0x01; This is used on TD only. It's read/write register but does not affect anything in the FPGA.

Bit 23-16 (R): Block size (block level). This is the block level used on the FPGA.

Bit 31-24 (R): Block size set by TS (or TImaster). This is an intermediate value.

- Address offset: 0x00018: TI data format control: Reset default 011; [0x00, BIT(31:29)]

- Bit 0: if '1', two block placeholder words are enabled; '0' disabled.

- Bit 2-1: Event format control:

- 00: Shortest words per trigger;

- 01: The TS timing word (bit 31-0) is enabled;

- 10: The TS timing word (bit 47-32) is enabled as lower 16-bit readout;

- 11: The TS timing word (bit(47:0) is enabled as two words;

- Bit 3: '1' to enable the GTP trigger input readout;

- Bit 4: '1' to enable the EXT (front panel synchronous) trigger inputs readout;

- Bit 5: '1' to enable the FP (front panel Asynchronous) trigger inputs readout;

- Address offset: 0x0001C: VME setting; Reset default 0x011:

- Bit 0 (R/W): '1' enable Bus\_Error\_En, so the block read can be terminated by event block trailer; [0x10, BIT(0)]

- Bit 1 (R/W): '1' en\_token\_in is true, '0' en\_token\_in is false; [0x10, BIT(1)]

- Bit 2 (R/W): '1' enable 'Multi-board' readout, '0' disable 'Multi-board'; [0x10, BIT(2)]; asset to enable multi-board token passing protocol;

- Bit 3 (R/W): '1' enable en\_A32m, '0' disable en\_A32m; [0x10, BIT(3)]; assert to enable common A32 multi-board addressing of module;

- Bit 4 (R/W): '1' enable en\_A32, '0' disable en\_A32; [0x10, BIT(4)]

- Bit 7 (R/W): '1' enable VME bus interrupt for module error? (not used)

- Bit 8 (R/W): '1' I2C device address 0x1101xxx, '0' I2C device address 0x0000xxx; [0x04, BIT8]

- Bit 9 (R/W): '1' token in high, '0' token in low; [0x04, BIT(9)]

- Bit 10 (R/W): '1' first board true, '0' first board false; [0x04, BIT(10)]

- Bit 11 (R/W): '1' last board true, '0' last board false; [0x04, BIT(11)]

- Bit 15 (R/W): '1' disable data readout buffer full [0x04, BIT(15)]

- Bit 16: Enable the front panel (external input) signal to latch the trigger input scalars;

- Bit 17: Enable the front panel (same signal as controlled by bit0) to reset the trigger input scalars; These two bits are kind of related to the OneShotVme command, offset 0x100, bit 24 and bit25.

- > Address offset: 0x00020: Trigger source register:

- Bit 15-0 (R/W): Trigger source enables: Reset default 0x0000; [0x00, BIT(23:16)]

- Bit 0: P0 trigger input;

- Bit 1: HFBR#1 trigger input;

- Bit 2: TS loopback trigger input; (No effect on TS)

- Bit 3: Front Panel trigger input; Bit 4: VME trigger; Bit 5: Front Panel Trigger Codes (as Supervisor) inputs; Bit 6: TS\_rev2 trigger input; Bit 7: Random Trigger. Bit 8: FP/Ext/GTP trigger enable on TS; Bit 9: P2 Busy used as Trigger input [0x28, BIT(6)] Bit 12: Enable SubTS#1 generation on TS; Bit 13: Enable SubTS#2 generation on TS; Bit 14: Enable SubTS#3 generation on TS; Bit 15: Enable SubTS#4 generation on TS;

- Bit 31-16 (R): Trigger source monitor.[0x00, BIT(31:24)]

- Address offset: 0x00024: Sync Source register:

Bit 15-0 (R/W): Sync Source enables: Reset default 0x02; [0x00, BIT(28:24)]

- Bit 0: P0 sync input;

- Bit 1: HFBR#1 sync input;

- Bit 2: HFBR#5 sync input;

- Bit 3: Front panel sync input;

- Bit 4: TS loopback SYNC enable;

- Bit 6: Automatic SyncReset enable;

- Bit 7: '1', Sync code 0x99 and 0xCC enable

- Bit 31-16 (R): Sync source monitoring.[0x28, BIT(23:16)]

- ➤ Address offset: 0x00028: Busy source registers:

Bit 15-0 (R/W): Busy source enables: [0x04, BIT(31:16)]

- Bit 0: '1' enable the Switch Slot #A BUSY input, '0' disable;

- Bit 1: '1' enable the Switch Slot #B BUSY input, '0' disable;

- Bit 2: '1' enable the VME P2 BUSY input, '0' disable;

- Bit 3: '1' enable the FTDC front panel BUSY input, '0' disable;

- Bit 4: '1' enable the FADC front panel BUSY input, '0' disable;

- Bit 5: '1' enable the Front Panel BUSY, which is the same as TsRev2 busy;

- Bit 6: '1' Use P2 BUSY input as trigger1 input (useful and valid for TD only);

- Bit 7: '1' enable TS feedback BUSY, '0' disable the busy. (useful in TM mode);

Bit 15-8: HFBR #8-#1 BUSY enables: '1' enable the HFBR BUSY input, '0' disable;

- Bit 8: TI\_A busy

- Bit9: TI\_B busy

- Bit10: TS data block readout interrupt N reaches 0x8000;

- Bit 31-16 (R): BUSY source monitoring. [0x28, BIT(15:0)]

- Bit (23-16): Busy bits(7:0) monitoring

- Bit 24: TI\_A data readout acknowledges lagged too much (over threshold);

- Bit 25: TI\_B data readout acknowledges lagged too much (over threshold);

- Bit 26: Interrupt counter Bit(15), that is too many interrupt waiting;

Bit 27: Internal loop back BUSY; Bit 28: TI\_A BUSY Bit 29: TI\_B BUSY

➤ Address offset: 0x0002C: Clock source selection:

Bit 1-0 (R/W): software bit switch to control the clock source. Reset default 00; [0x08, BIT(13:12)]

Bit[1:0] = 00: oscillator clock;

Bit[1:0] = 01: HFBR#5 clock input; (not valid for current setup)

Bit[1:0] = 10: HFBR#1 clock input;

Bit[1:0] = 11: Front panel 34-pin connector clock input.

00, 11: oscillator clock on TS;

01, 10: SMA external clock input on TS;

Address offset: 0x00030: Trigger\_1 pre-scale:

Bit 15-0 (R/W): pre-scale factor: Rate = Rate\_0 / (Bit(15:0)+1). [0x0C, BIT(31:28)]

- Address offset: 0x00034: Trigger block inhibit:

- Bit 7-0 (R/W): TS trigger inhibit threshold (in the unit of event blocks); Reset default 0x01; [0x08, BIT(31:24)]

- Bit 23-8 (R): Number of blocks in the DAQ ready to be readout. [0x14, BIT(31:24)]

- (on TI, Bit 23-16 (R): Number of events before the a block is formed. [0x14, BIT(23:16)])

- Bit 27-24 (R): Number of missing block acknowledge;

- Bit 28 (R): if '1', the run stopped because the number of block (readout) has reached (set by 0xFC);

Bit 29 (R): if '1', the event block is being filled by FillTrg;

- Bit 30 (R): SyncReset requested, waiting for TS CPU to issue SyncReset;

- Bit 31 (R): SyncEvent received, and the system is BUSY. Waiting for ROC to clear the frontend data.

- Address offset: 0x00038: Trigger rules:

- Bit 7-0 (R/W): No more than 1 Trigger in (Bit(6:0)\*(16/500 ns)); Bit7 determines 16ns or 500ns step. Reset default 0x03; [R:0x58, BIT(23:16)] [W:0x810, BIT(7:0)]

- Bit 15-8 (R/W): no more than 2 trigger in (Bit(14:8)\*(16/500ns)); Bit15 determines 16ns or 500ns step. Reset default 0x03; [W:0x810, BIT(15:8)]

- Bit 23-16 (R/W): no more than 3 triggers in (Bit(22:16)\*(16/500 ns)); Bit23 determines 16ns or 500ns step. Reset default 0x03; [R:0x58, BIT(31:24)] [W:0x810, BIT(23:16)]

- Bit 31-24 (R/W): no more than 4 triggers in (Bit(30:24)\*(16/500 ns)). Bit31 determines 16ns or 500ns step. Reset default 0x03; [W:0x810, BIT(31:24)]

- Address offset: 0x0003C: Trigger coincidence window:

Bit 7-0 (R/W): Trigger input coincidence window; Reset default 0x01; Bit15-8 (R/W): Trigger inhibit window (extra to bit(7:0)). Reset default 0x00; These two parameters are used to determine the event resolution

Address offset: 0x00040: GTP trigger input enable:

Bit 31-0 (R/W): 32-bit GTP input enables. Reset default 0x00000000; 23

> Address offset: 0x00044: Front panel external trigger input enable:

Bit 31-0 (R/W): Front panel 32-bit external trigger input enable. Reset default 0x00000000;

- Address offset: 0x00048: Front panel generic trigger input enable:

- Bit 15-0 (R/W): Front panel generic trigger input enable (34-pin TI). Reset default 0x00000000; [0x08, BIT(21:16)]

- Address offset: 0x0004C: Blocks for VME interrupt:

- Bit 15-0 (R/W): 4-bit output to the front panel generic output connector; Reset default 0x0000; [0x2C, BIT(3:0)]

- Bit 23-16 (R): Number of data blocks ready for VME interrupts. [0x2C, BIT(31:24)]

Bit 31-24 (R): on TI: Number of events of a partial block (or, before the block is formed) On TS: bit(15:8) of the number of data blocks ready for VME interrupt.

Address offset: 0x00050: Sync delay setting (to compensate for the fiber length):

Bit 7-0 (R): on TI: SYNC phase of HFBR#1 input; [0x1C, BIT(7:0)] Bit 15-8 (R/W): HFBR#1 SYNC input delay; Reset default 0x00; [0x1C, BIT(15:8)] Bit 23-16 (R/W): TM (internal loopback) SYNC delay; Reset default 0x00; [0x1C, BIT(23:16)] Bit 23-16 (R): on TI: SYNC phase of HFBR#5 input; [0x1C, BIT(23:16)] Bit(31:24 (R/W): HFBR#5 SYNC input delay. Reset default 0x00; [0x1C, BIT(31:24)]

> Address offset: 0x00054: GTP input pre-scale: Reset default 0x00000000;

Bit 3-0 (R/W): GTP input #1 pre-scale; Bit 7-4 (R/W): GTP input #2 pre-scale; Bit 11-8 (R/W): GTP input #3 pre-scale; Bit 15-12 (R/W): GTP input #4 pre-scale; Bit 19-16 (R/W): GTP input #5 pre-scale; Bit 23-20 (R/W): GTP input #6 pre-scale; Bit 27-24 (R/W): GTP input #7 pre-scale; Bit 31-28 (R/W): GTP input #8 pre-scale.

> Address offset: 0x00058: GTP input pre-scale: Reset default 0x00000000;

Bit 3-0 (R/W): GTP input #9 pre-scale; Bit 7-4 (R/W): GTP input #10 pre-scale; Bit 11-8 (R/W): GTP input #11 pre-scale; Bit 15-12 (R/W): GTP input #12 pre-scale; Bit 19-16 (R/W): GTP input #13 pre-scale; Bit 23-20 (R/W): GTP input #14 pre-scale; Bit 27-24 (R/W): GTP input #15 pre-scale; Bit 31-28 (R/W): GTP input #16 pre-scale.

> Address offset: 0x0005C: GTP input pre-scale: Reset default 0x00000000;

Bit 3-0 (R/W): GTP input #17 pre-scale;

Bit 7-4 (R/W): GTP input #18 pre-scale; Bit 11-8 (R/W): GTP input #19 pre-scale; Bit 15-12 (R/W): GTP input #20 pre-scale; Bit 19-16 (R/W): GTP input #21 pre-scale; Bit 23-20 (R/W): GTP input #22 pre-scale; Bit 27-24 (R/W): GTP input #23 pre-scale; Bit 31-28 (R/W): GTP input #24 pre-scale.

Address offset: 0x00060: GTP input pre-scale: Reset default 0x00000000;

Bit 3-0 (R/W): GTP input #25 pre-scale; Bit 7-4 (R/W): GTP input #26 pre-scale; Bit 11-8 (R/W): GTP input #27 pre-scale; Bit 15-12 (R/W): GTP input #28 pre-scale; Bit 19-16 (R/W): GTP input #29 pre-scale; Bit 23-20 (R/W): GTP input #30 pre-scale; Bit 27-24 (R/W): GTP input #31 pre-scale; Bit 31-28 (R/W): GTP input #32 pre-scale.

> Address offset: 0x00064: Front Panel external trigger input pre-scale: Reset default 0x00000000

Bit 3-0 (R/W): FP external trigger input #1, B#1 pre-scale; Bit 7-4 (R/W): FP external trigger input #2, B#2 pre-scale; Bit 11-8 (R/W): FP external trigger input #3, B#3 pre-scale; Bit 15-12 (R/W): FP external trigger input #4, B#4 pre-scale; Bit 19-16 (R/W): FP external trigger input #5, B#5 pre-scale; Bit 23-20 (R/W): FP external trigger input #6, B#6 pre-scale; Bit 27-24 (R/W): FP external trigger input #7, B#7 pre-scale; Bit 31-28 (R/W): FP external trigger input #8, B#8 pre-scale.

> Address offset: 0x00068: Front Panel external trigger input pre-scale: Reset default 0x00000000

Bit 3-0 (R/W): FP external trigger input #9, A#1 pre-scale; Bit 7-4 (R/W): FP external trigger input #10, A#2 pre-scale; Bit 11-8 (R/W): FP external trigger input #11, A#3 pre-scale; Bit 15-12 (R/W): FP external trigger input #12, A#4 pre-scale; Bit 19-16 (R/W): FP external trigger input #13, A#5 pre-scale; Bit 23-20 (R/W): FP external trigger input #14, A#6 pre-scale; Bit 27-24 (R/W): FP external trigger input #15, A#7 pre-scale; Bit 31-28 (R/W): FP external trigger input #16, A#8 pre-scale.

Address offset: 0x0006C: Front Panel external trigger input pre-scale: Reset default 0x00000000

Bit 3-0 (R/W): FP external trigger input #17, D#1 pre-scale; Bit 7-4 (R/W): FP external trigger input #18, D#2 pre-scale; Bit 11-8 (R/W): FP external trigger input #19, D#3 pre-scale; Bit 15-12 (R/W): FP external trigger input #20, D#4 pre-scale; Bit 19-16 (R/W): FP external trigger input #21, D#5 pre-scale; Bit 23-20 (R/W): FP external trigger input #22, D#6 pre-scale; Bit 27-24 (R/W): FP external trigger input #23, D#7 pre-scale; Bit 31-28 (R/W): FP external trigger input #24, D#8 pre-scale.

Address offset: 0x00070: Front Panel external trigger input pre-scale: Reset default 0x00000000

Bit 3-0 (R/W): FP external trigger input #25, C#1 pre-scale; Bit 7-4 (R/W): FP external trigger input #26, C#2 pre-scale; Bit 11-8 (R/W): FP external trigger input #27, C#3 pre-scale; Bit 15-12 (R/W): FP external trigger input #28, C#4 pre-scale; Bit 19-16 (R/W): FP external trigger input #29, C#5 pre-scale; Bit 23-20 (R/W): FP external trigger input #30, C#6 pre-scale; Bit 27-24 (R/W): FP external trigger input #31, C#7 pre-scale; Bit 31-28 (R/W): FP external trigger input #32, C#8 pre-scale.

Address offset: 0x00074: Front Panel generic trigger input pre-scale: Reset default 0x00000000

Bit 3-0 (R/W): FP Generic trigger input #1 and #9 pre-scale; (#1 is not trigger input, it is INHIBIT) Bit 7-4 (R/W): FP Generic trigger input #2 and #10 pre-scale; Bit 11-8 (R/W): FP Generic trigger input #3 and #11 pre-scale; Bit 15-12 (R/W): FP Generic trigger input #4 and #12 pre-scale; Bit 19-16 (R/W): FP Generic trigger input #5 and #13 pre-scale; Bit 23-20 (R/W): FP Generic trigger input #6 and #14 pre-scale; Bit 27-24 (R/W): FP Generic trigger input #7 and #15 pre-scale; Bit 31-28 (R/W): FP Generic trigger input #8 and #16 pre-scale.

Address offset: 0x00078: VME Sync Load[0x900, BIT(7:0)]

Bit 7-4 == Bit 3-0 (R/W): 4-bit sync code; Decoding of the Sync command (bit[7:0]):

- 0x11: VME clock DCM reset, and full reset;

- 0x22: CLK250 resync (AD9510, DCM resync and MGT reset);

- 0x33: AD9510 re-sync (slower clock phase adjustment), part of 0x22 function;

- 0x44: Reset the MGT status\_B registers;

- 0x55: Trigger link enable (serial link started), FIFO read counter reset;

- 0x77: Trigger link disable, trigger FIFO write counter reset;

- 0xAA: reset the TI\_trigger\_enabled registers on TD.

- 0xBB: Event number reset, and trigger input scalar reset;

- 0xDD: (SyncReset), FPGA logic and counter reset, this reset all goes to SD, CTP/GTP;

- 0x99: Force SyncReset high if this feature is enabled (by offset 0x24, bit 7);

- 0xCC: set the SyncReset low if it is forced high by code 0x99.

- 0x66, 0x88, 0xee: to be assigned;

- 0x00, 0xff: reserved, not to be assigned

- Address offset: 0x0007C: VME Sync Delay. The latency before being serialized.

Bit 6-0 (R/W): latency, in 4ns steps. Reset default 000,0111 [0x904, BIT(6:0)]

- Address offset: 0x00080: Reset pulse width: Reset default 00,0111

- Bit 7-0 (R/W): Reset (to SW#A, SW#B and on-board) pulse width. Pulse width is (Bit(6:0)\*(4/32 ns)), Bit(7) determines the steps (4ns or 32ns); [0x904, BIT(13:8), bit(13) set to pulse to 1us wide]

- Address offset: 0x00084: VME Trigger Command Register

Bit 11-0 (R/W): Trigger Command code transmitted in the trigger link; In the 12 bits, 0xABC, the 0xA determines the command type. For example:

Bit(11-0) = 0x123: (A=1) one trigger1 (readout trigger) pulse will be generated, and the event type = 0x23;

Bit(11-0) = 0x221: (A=2) one trigger2 pulse will be generated. The 0x21 is ignored;

Bit(11-0) = 0x812: (A=8) Set the block level (size), and the block level is set to 0x12.

Address offset: 0x00088 (R/W): VME Random Trigger Command Register: [0x808, BIT(15:0)]

Bit 3-0: Random trigger\_1 rates: 500KHz/(2<sup>Bit(3:0)</sup>); Bit 6-4: same as Bit(2-0) for redundancy check. No match, no trigger\_1; Bit 7: enable/disable random trigger\_1; Bit (7:0) = 0x80 for highest rate (~500 kHz), and 0xFF for lowest rate (~15 Hz). Bit 11-8: Random trigger\_2 rates: 500KHz/(2<sup>Bit(11:8)</sup>); Bit 14-12: same as Bit(10-8) for redundancy check. No match, no trigger\_2. Bit 15: enable/disable random trigger\_2;

Address offset: 0x0008C(R/W): VME Trigger Generation: [0x804, BIT(31:0)]

Bit 15-0: Number of trigger\_1s to be generated; Bit 31-16: (trigger rate control) Time between triggers.  $T = (120+30*Bit(30:16)*1024^{Bit(31)})$  ns. (Assuming that the ClkVme=33MHz or 30ns period).

Address offset: 0x00090(R/W): VME Trigger\_2 Generation: [0x80C, BIT(31:0)]

Bit 15-0: Number of trigger\_2s to be generated;

Bit 31-16: (trigger rate control) Time between triggers.  $T = (120+30*Bit(30:16)*1024^{Bit(31)})$  ns. (Assuming that the ClkVme=33MHz or 30ns period).

Address offset: 0x00094 (R): Number of Blocks in the DAQ system: [0x14, BIT(15:0)]

Bit 31-24: Number of events of a partial data block;

Bit 23-0: Number of full data blocks the TIDS has ever generated;

Address offset: 0x00098 (R): SYNC command history;

Bit 3:0: SYNC command that the TS has ever received; "0000" if the history buffer is empty.

- Address offset: 0x0009C (R/W): The FPGA running mode;

- Bit 7-0: TS in running mode if set to 0x5A; if other value, not in running mode. Reset default 0x00; TI in running mode if set to 0x71. TI starts clock monitoring in 'running' mode.

- Address offset: 0x000A0 (R): Fiber latency measurement result: [0x18]

Bit 31-23: latency data in 4ns steps Bit 22-16: Delay in the IODelay, in 5000/64=78.125ps steps 27 Bit 15:0: Delay in the carry chain, two bits per slice, (or two mux per bit)

- Address offset: 0x000A4 (R): Fiber SYNC delay and phase alignment: [0x1C] (kind of repeat of 0x50)

- Bit 31-24: HFBR#5 sync delay; Bit 23-16: HFBR#5 IODelay, for phase adjustment; Bit 15-8: HFBR#1 Sync delay (in 4ns steps); Bit 7-0: HFBR#1 IODelay, for phase adjustment.

- Address offset: 0x000A8 (R): Trigger live timer: [0x20]

Bit 31-0 (r): board live time counter. The real time is Bit(31:0)\*256\*30ns.

- Address offset: 0x000AC (R): Trigger busy (trigger dead) timer: [0x24]

- Bit 31-0 (r): TID busy (cannot accept trigger, or trigger dead) time counter. The real time is Bit(31:0)\*256\*30ns. This counter and the live time counter make up the total time counter, which is the total time since any one of the trigger sources is enabled.

- Address offset: 0x000B0 (R): MGT STATUS\_A: [0x30]

Bit 7-0: MGT[7:0] reset done; Bit 11-8: MGT PLL lock detected (two MGTs per PLL lock); Bit 31-12 : not used yet;}

Address offset: 0x000B4 (R): MGT STATUS\_B registers: [0x34]

Bit 7-0: Channel bonding sequence detected in MGT[7:0]; Bit 15-8: received data is not an 8B/10B character, or has disparity error in MGT[7:0]; Bit 23-16: RX disparity error has occurred in MGT[7:0]; Bit 31-24: Rx data not in 8B/10B table has occurred in MGT[7:0].

- Address offset: 0x000B8 (R): MGT trigger data buffer length: [0x38]

- Bit 9-0: Global trigger data buffer length (to be minimized to 0 for the longest fiber);

- Bit 11-10: Data generation fifo full (in TRGDAQ module);

- Bit 13-12: Data Readout fifo prog\_almost\_full (in VME module);

- Bit 15:14: Data Readout fifo full; The order should be: DataReadoutFifoProgFull → DataGenFifoFull → DataReadoutFifoFull

- Bit 25-16: Sub-system trigger data buffer length;

- Bit 27: TI is in running mode if '1';

- Bit 28: HFBR#1 MGT receiver error;

- Bit 29: CLK250 DCM locked;

- Bit 30: Clk125 DCM locked;

- Bit 31: VME CLK (33MHz or 25MHz) DCM locked

- Address offset: 0x000BC (R): TS input trigger counter: [0x3C]

Bit 31-0: Number of triggers received by TS (before BUSY inhibits).

Address offset: 0x000C0 (R): valid for TM (or with TS function), not valid for TI: [0x40]

Bit 7-0: Number of blocks to be readout on HFBR#1;

Bit 15-8: Number of blocks is still missing on HFBR#1

Bit 23-16: Number of blocks to be readout on HFBR#2

Bit 31-24: Number of blocks is still missing on HFBR#2

Address offset: 0x000C4 (R): valid for TM (or with TS function), not valid for TI: [0x44]

Bit 7-0: Number of blocks to be readout on HFBR#3;Bit 15-8: Number of blocks is still missing on HFBR#3;Bit 23-16: Number of blocks to be readout on HFBR#4;Bit 31-24: Number of blocks is still missing on HFBR#4;For TS, Bit 31-0: External Trigger counter, Number of triggers from External trigger before lookup table.

Address offset: 0x000C8 (R): valid for TM (or with TS function), not valid for TI: [0x48]

Bit 7-0: Number of blocks to be readout on HFBR#5; Bit 15-8: Number of blocks is still missing on HFBR#5; Bit 23-16: Number of blocks to be readout on HFBR#6; Bit 31-24: Number of blocks is still missing on HFBR#6; For TS, Bit 31-0: Front Panel Trigger counter, Number of triggers from FP trigger before lookup table.

Address offset: 0x000CC (R): valid for TM (or with TS function), not valid for TI: [0x4C]

Bit 7-0: Number of blocks to be readout on HFBR#7; Bit 15-8: Number of blocks is still missing on HFBR#7; Bit 23-16: Number of blocks to be readout on HFBR#8; Bit 31-24: Number of blocks is still missing on HFBR#8;

Address offset: 0x000D0 (R): valid for TM (or with TS function)

Bit 4-0: A24 address used for the module (to match with A23-A19); [0x54, BIT(4:0)] Bit 9-5: A24 address set by the onboard hardware switch; [0x54, BIT(9:5)] Bit 14-10: GA(4:0), VME64x geographic address; [0x54, BIT(14:10)] Bit 15: parity of GA(4:0); [0x54, BIT15] Bit 27-16: Number of blocks to be readout on TM itself; [0x50, BIT(23:16)] Bit 31-28: Number of blocks is still missing on TM itself; [0x50, BIT(31:24)]

> Address offset: 0x000D4 (R/W): Periodic Sync Event register

Bit 15-0: Number of data blocks to assert a sync event; Bit 23-16: Sync event enable if set to 0x5A;

> Address offset: 0x000D8: TIA/TIB optic transceiver modules status and Event number;

Bit 0 (r/w): Fiber module #A select, '1' to select;

Bit 1 (r/w): Fiber module #B select, '1' to select if #A is NOT selected;

Bit 4 (r): Fiber # A transceiver present, '0' means present;

Bit 5 (r): Fiber # A interrupt, '0' means interrupt requested;

Bit 6 (r): Fiber # B transceiver present, '0' means present;

Bit 7 (r): Fiber # B interrupt, '0' means interrupt requested;

Bit 31-16 (r): Higher 16 bits of the L1 trigger number (event number)

➤ Address offset: 0x000DC (R): Event number

Bit 31-0: Lower 32 bits of the L1 trigger number (event number).

Address offset: 0x000E0 (R): TI#A ID

Bit 7-0: TI#A Trigger Source Enable; Bit 15-8: TI#A Crate ID.

➤ Address offset: 0x000E4 (R): TI#B ID

Bit 7-0: TI#B Trigger Source Enable; Bit 15-8: TI#B Crate ID.

➤ Address offset: 0x000E8 (R): TS ID

Bit 7-0: TS (itself) Trigger Source Enable, should be the same as bit7-0 of offset 0x20; Bit 15-8: TS (itself) Crate ID, should be the same as bit7-0 of offset 0x00.

- Address offset: 0x000EC: not used yet

- > Address offset: 0x000F0 (R): valid for TM (or with TS function)

Bit 31-0: Number of valid code from Front Panel Async trigger inputs

➤ Address offset: 0x000F4 (R): valid for TS

Bit 31-0: Number of valid code from GTP trigger inputs

➤ Address offset: 0x000F8 (R): valid for TS

Bit 31-0: Number of valid code from Front Panel sync trigger (External) inputs

Address offset: 0x000FC (R/W): End\_of\_run block number limit

Bit 31-0: when the limit reached, the trigger is disabled automatically.

- Address offset: 0x00100 (W): Reset and one-shot registers. The signal will be one ClkVme cycle. If the ClkVme is 33 MHz, the one-shot will be 30ns wide. Positive logic. [0x100]

- Bit 0: not used;

- Bit 1: if '1', RESET signal to reset the VME\_to\_I2C engine;

- Bit 2: if '1', RESET signal to reset the VME\_to\_JTAG engine;

- Bit 3: if '1', RESET signal to reset the VME\_to\_SFM engine;

- Bit 4: if '1', RESET signal to reset the VME registers (TID settings) to their default values;

- Bit 5: if '1', RESET signal to reset the fiber optic transceivers; (only for TS rev2 and later)

- Bit 6: if '1', clear the SYNC command history buffer;

- Bit 7: if '1', this register will generate a BUSY reset, and Trg\_Ack pulse (TS rev2 compatible).

- Bit 8: if '1', Reset the CLK250/Clk200 DCM.

- Bit 9: if '1', Reset the CLK125 DCM.

- Bit 10: if '1', Reset the MGT (MultiGigabit Transceiver,) inside the FPGA.

- Bit 11: if '1', Auto alignment of SYNC phase from HFBR#1; auto align P0 sync input for TD.

- Bit 12: if '1', TI: Auto alignment of SYNC phase from HFBR#5;

- TS: reset the BRAM loading address to 0 (very beginning).

- Bit 13: if '1', Auto alignment of fiber latency measurement signals;

- Bit 14: if '1', Reset the IODELAY;

- Bit 15: if '1', Measure the fiber latency

- Bit 16: if '1', this register will generate a 'TAKE\_TOKEN'

- Bit 17: if '1', the available number of data blocks will decrease by 1,

- Bit 20: if '1', Force a sync event with event type 0,

- Bit 23: if '1', indicates that the TS data is out of sync, and Sync\_Reset is required;

- Bit 24: if '1', all the trigger input scalars are latched (ready for read out), The livetimer/busytimer are latched;

- Bit 25: if '1', all the trigger input scalars are reset. (Bit 24 and Bit 25 can be set simultaneously); The event number (L1A trigger counter) is reset

- Bit 26: if '1', this register will generate a SubTS#1 ROC acknowledgement; (comparison: Bit 7: for TS)

- Bit 27: if '1', this register will generate a SubTS#2 ROC acknowledgement;

- Bit 28: if '1', this register will generate a SubTS#3 ROC acknowledgement;

- Bit 29: if '1', this register will generate a SubTS#4 ROC acknowledgement;

- Bit 31: if '1', the end\_of\_run command. If the readout block is not full, dummy trigger will be generated to fill the block.

- Address offset: 0x008CX (0x8C0 0x8FC) (W): Trigger table loading: (prototype TS / TImaster) [0x8CX]

Bit 31-0: 32-bit wide table loading.

Address bits(5-2) are used to load 16 32-bit words;

6-bit read addressing with 8-bit trigger type (byte wide)

Address offset: 0x134 (R): SubTS#1 Data ready polling register (reg 0x34: for TS)

Bit 31-24: SubTS#1 number of event before forming a data block. Bit 23-8: SubTS#1 number of blocks of data to be read out (to be acknowledged). Bit 7-0: number of events per block (block level).

Address offset: 0x140 (R/W): SubTS#1 Front Panel Async trigger input selection

Bit 17-12: SubTS#1 trigger signal #13 source selections from FP inputs.

Bit 11-6: SubTS#1 trigger signal #12 source selections from FP inputs.

Bit 5-0: SubTS#1 trigger signal #11 source selection from FP inputs.

When '010001', VME periodic trigger is selected;

When '010010', Random trigger is selected.

This is true for 0x340, 0x540 and 0x740 registers too.

Address offset: 0x144 (R/W): SubTS#1 GTP trigger input selection

Bit 29-24: SubTS#1 trigger signal #5 source selection from GTP inputs. Bit 23-18: SubTS#1 trigger signal #4 source selection from GTP inputs. Bit 17-12: SubTS#1 trigger signal #3 source selection from GTP inputs. Bit 11-6: SubTS#1 trigger signal #2 source selection from GTP inputs. Bit 5-0: SubTS#1 trigger signal #1 source selection from GTP inputs.

Address offset: 0x148 (R/W): SubTS#1 Front Panel External Sync trigger input selection

Bit 29-24: SubTS#1 trigger signal #10 source selection from EXT inputs. Bit 23-18: SubTS#1 trigger signal #9 source selection from EXT inputs. Bit 17-12: SubTS#1 trigger signal #8 source selection from EXT inputs. Bit 11-6: SubTS#1 trigger signal #7 source selection from EXT inputs. Bit 5-0: SubTS#1 trigger signal #6 source selection from EXT inputs.

➤ Address offset: 0x14C (W): SubTS#1 lookup table loading

Bit 31-0: SubTS#1 lookup table context. 1024 operations are required for one Block RAM loading.

Address offset: 0x150 (R): SubTS#1 data readout

Bit 31-0: SubTS#1 event data.

> Address offset: 0x154 (R): SubTS#1 Data Block available register

Bit 31-24: SubTS#1 number of event before forming an data block. Bit 23-8: SubTS#1 number of blocks of data generated. Bit 7-0: SubTS#1 number of data blocks to be read out.

- ➤ Address offset: 0x158 (R/W): SubTS#1 Busy setting

- Bit 31-24: SubTS#1: buffer threshold for number of data blocks on TS.

- Bit 23: TI\_B busy enable (in case that the TI\_B is configured as partition SubTS #1);

- Bit 22: TI\_A busy enable (in case that the TI\_A is configured as partition subTS#1);

- Bit 21: Front panel inhibit enable;

- Bit 20: VXS switch slot#B busy enable;

- Bit 17: SubTS#1: '1' enables the number of data block threshold.

- Bit 16: SubTS#1: '1' enable the data fifo Programmable\_almost\_full backpressure.

- Bit 15-0: SubTS#1: TD\_busy input 15-0 enables for SubTS#1 (or, is this TD belong to SubTS#1)

- ➢ Address offset: 0x15C (R): SubTS#1 Busy time

Bit 15-0: SubTS#1: Busy time. Busy percentage: Bit(15-0)/0xf000; This number is updated ~every second

Address offset: 0x00180 (R): FP input trigger scalar for #1 (INHIBIT, not valid):

Bit 31-0: 32-bit scalar, number of input counter

> Address offset: 0x00184 (R): FP input trigger scalar for #2:

Bit 31-0: 32-bit scalar, number of FP input#2 counter

Address offset: 0x00188 (R): FP input trigger scalar for #3:

Bit 31-0: 32-bit scalar, number of FP input#3 counter

Address offset: 0x0018C (R): FP input trigger scalar for #4:

Bit 31-0: 32-bit scalar, number of FP input#4 counter

- Address offset: 0x00190 (R): GTP input trigger scalar for #1 (clock, not valid):

Bit 31-0: 32-bit scalar, number of GTP input#1 counter

- Address offset: 0x00194 (R): GTP input trigger scalar for #2:

Bit 31-0: 32-bit scalar, number of GTP input#2 counter

- Address offset: 0x00198 (R): GTP input trigger scalar for #3: Bit 31-0: 32-bit scalar, number of GTP input#3 counter

- Address offset: 0x0019C (R): GTP input trigger scalar for #4:

Bit 31-0: 32-bit scalar, number of GTP input#4 counter

- Address offset: 0x001A0 (R): GTP input trigger scalar for #5:

Bit 31-0: 32-bit scalar, number of GTP input#5 counter

- Address offset: 0x001A4 (R): GTP input trigger scalar for #6:

Bit 31-0: 32-bit scalar, number of GTP input#6 counter

- Address offset: 0x001A8 (R): GTP input trigger scalar for #7:

Bit 31-0: 32-bit scalar, number of GTP input#7 counter

- Address offset: 0x001AC (R): GTP input trigger scalar for #8:

Bit 31-0: 32-bit scalar, number of GTP input#8 counter

- Address offset: 0x001B0 (R): External input trigger scalar for #1 (B1):

Bit 31-0: 32-bit scalar, number of External trigger input#1 counter

- Address offset: 0x001B4 (R): External input trigger scalar for #2 (B2):

Bit 31-0: 32-bit scalar, number of External trigger input#2 counter

- Address offset: 0x001B8 (R): External input trigger scalar for #3 (B3):

Bit 31-0: 32-bit scalar, number of External trigger input#3 counter

- Address offset: 0x001BC (R): External input trigger scalar for #4 (B4):

Bit 31-0: 32-bit scalar, number of External trigger input#4 counter

- Address offset: 0x001C0 (R): External input trigger scalar for #5 (B5):

Bit 31-0: 32-bit scalar, number of External trigger input#5 counter

- Address offset: 0x001C4 (R): External input trigger scalar for #6 (B6):

Bit 31-0: 32-bit scalar, number of External trigger input#6 counter

- Address offset: 0x001C8 (R): External input trigger scalar for #7 (B7):

33

Bit 31-0: 32-bit scalar, number of External trigger input#7 counter

Address offset: 0x001CC (R): External input trigger scalar for #8 (B8):

Bit 31-0: 32-bit scalar, number of External trigger input#8 counter

Address offset: 0x334 (R): SubTS#2 Data ready polling register (reg 0x34: for TS)

Bit 31-24: SubTS#2 number of event before forming a data block. Bit 23-8: SubTS#2 number of blocks of data to be read out (to be acknowledged). Bit 7-0: number of events per block (block level).

Address offset: 0x340 (R/W): SubTS#2 Front Panel Async trigger input selection

Bit 17-12: SubTS#2 trigger signal #13 source selection from FP inputs.

Bit 11-6: SubTS#2 trigger signal #12 source selection from FP inputs.

Bit 5-0: SubTS#2 trigger signal #11 source selection from FP inputs.

When '010001', VME periodic trigger is selected;

When '010010', Random trigger is selected.

Address offset: 0x344 (R/W): SubTS#2 GTP trigger input selection

Bit 29-24: SubTS#2 trigger signal #5 source selection from GTP inputs. Bit 23-18: SubTS#2 trigger signal #4 source selection from GTP inputs. Bit 17-12: SubTS#2 trigger signal #3 source selection from GTP inputs. Bit 11-6: SubTS#2 trigger signal #2 source selection from GTP inputs. Bit 5-0: SubTS#2 trigger signal #1 source selection from GTP inputs.

Address offset: 0x348 (R/W): SubTS#2 Front Panel External Sync trigger input selection

Bit 29-24: SubTS#2 trigger signal #10 source selection from EXT inputs. Bit 23-18: SubTS#2 trigger signal #9 source selection from EXT inputs. Bit 17-12: SubTS#2 trigger signal #8 source selection from EXT inputs. Bit 11-6: SubTS#2 trigger signal #7 source selection from EXT inputs. Bit 5-0: SubTS#2 trigger signal #6 source selection from EXT inputs.

Address offset: 0x34C (W): SubTS#2 lookup table loading

Bit 31-0: SubTS#2 lookup table context. 1024 operations are required for one Block RAM loading.

Address offset: 0x350 (R): SubTS#2 data readout

Bit 31-0: SubTS#2 event data.

Address offset: 0x354 (R): SubTS#2 Data Block available register

Bit 31-24: SubTS#2 number of event before forming an data block. Bit 23-8: SubTS#2 number of blocks of data generated. Bit 7-0: SubTS#2 number of data blocks to be read out.

➤ Address offset: 0x358 (R/W): SubTS#2 Busy setting

- Bit 31-24: SubTS#2: buffer threshold for number of data blocks on TS.

Bit 23: TI\_B busy enable (in case that the TI\_B is configured as partition SubTS #2);

Bit 22: TI\_A busy enable (in case that the TI\_A is configured as partition subTS#2);

Bit 21: Front panel inhibit enable;

Bit 20: VXS switch slot#B busy enable;

Bit 17: SubTS#2: '1' enables the number of data block threshold.

Bit 16: SubTS#2: '1' enable the data fifo Programmable\_almost\_full backpressure.

Bit 15-0: SubTS#2: TD\_busy input 15-0 enables for SubTS#2 (or, is this TD belong to SubTS#2)

- ➢ Address offset: 0x35C (R): SubTS#2 Busy time

Bit 15-0: SubTS#2: Busy time. Busy percentage: Bit(15-0)/0xf000; This number is updated ~every second

- Address offset: 0x00380 (R): FP input trigger scalar for #5:

Bit 31-0: 32-bit scalar, number of FP input#5 counter

- Address offset: 0x00384 (R): FP input trigger scalar for #6:

Bit 31-0: 32-bit scalar, number of FP input#6 counter

- Address offset: 0x00388 (R): FP input trigger scalar for #7:

Bit 31-0: 32-bit scalar, number of FP input#7 counter

- Address offset: 0x0038C (R): FP input trigger scalar for #8:

Bit 31-0: 32-bit scalar, number of FP input#8 counter

- Address offset: 0x00390 (R): GTP input trigger scalar for #9:

Bit 31-0: 32-bit scalar, number of GTP input#9 counter

- Address offset: 0x00394 (R): GTP input trigger scalar for #10:

Bit 31-0: 32-bit scalar, number of GTP input#10 counter

- Address offset: 0x00398 (R): GTP input trigger scalar for #11:

Bit 31-0: 32-bit scalar, number of GTP input#11 counter

- Address offset: 0x0039C (R): GTP input trigger scalar for #12:

Bit 31-0: 32-bit scalar, number of GTP input#12 counter

- Address offset: 0x003A0 (R): GTP input trigger scalar for #13:

Bit 31-0: 32-bit scalar, number of GTP input#3 counter

- Address offset: 0x003A4 (R): GTP input trigger scalar for #14:

Bit 31-0: 32-bit scalar, number of GTP input#14 counter

- Address offset: 0x003A8 (R): GTP input trigger scalar for #15:

Bit 31-0: 32-bit scalar, number of GTP input#15 counter

- Address offset: 0x003AC (R): GTP input trigger scalar for #16:

Bit 31-0: 32-bit scalar, number of GTP input#16 counter

- Address offset: 0x003B0 (R): External input trigger scalar for #9 (A1):

Bit 31-0: 32-bit scalar, number of External trigger input#9 counter

- Address offset: 0x003B4 (R): External input trigger scalar for #10 (A2):

Bit 31-0: 32-bit scalar, number of External trigger input#10 counter

- Address offset: 0x003B8 (R): External input trigger scalar for #11 (A3):

Bit 31-0: 32-bit scalar, number of External trigger input#11 counter

- Address offset: 0x003BC (R): External input trigger scalar for #12 (A4):

Bit 31-0: 32-bit scalar, number of External trigger input#12 counter

- Address offset: 0x003C0 (R): External input trigger scalar for #13 (A5):

Bit 31-0: 32-bit scalar, number of External trigger input#13 counter

- Address offset: 0x003C4 (R): External input trigger scalar for #14 (A6):

Bit 31-0: 32-bit scalar, number of External trigger input#14 counter

- Address offset: 0x003C8 (R): External input trigger scalar for #15 (A7):

Bit 31-0: 32-bit scalar, number of External trigger input#15 counter

- Address offset: 0x003CC (R): External input trigger scalar for #16 (A8):

Bit 31-0: 32-bit scalar, number of External trigger input#16 counter

- Address offset: 0x534 (R): SubTS#3 Data ready polling register (reg 0x34: for TS)

Bit 31-24: SubTS#3 number of event before forming a data block.

Bit 23-8: SubTS#3 number of blocks of data to be read out (to be acknowledged).

Bit 7-0: number of events per block (block level).