Nuclear Physics Division Fast Electronics Group

# **VTP Manual**

Benjamin Raydo Chris Cuevas Bryan Moffitt Dave Abbott

Oct 9, 2023

### 1 Introduction

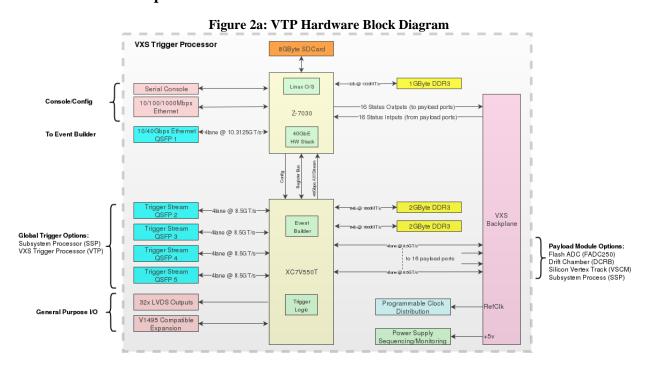

The VXS Trigger Processor (VTP) module is a VXS switch card module that participates in the Level 1 trigger in front-end VXS crates (a.k.a. the CTP switch slot) as well as the global-trigger VXS crate (a.k.a. the GTP switch slot). The VTP design supersedes the CTP and GTP designs as it contains more backplane serial links to front-end payload modules, more fiber optics serial links to other crates, and more FPGA resources for trigger logic. Additionally it contains a dual-core 1GHz ARM processor core that runs a CODA ROC on a Linux O/S capable of event building trigger diagnostic information from FPGA trigger logic. The processor utilizes 1Gbps Ethernet connection for configuration, control, and filesystem. Additionally a 10Gbps and 40Gbps Ethernet can be used for the CODA ROC readout in a future firmware/software development. This high speed readout can be used to read from compatible Jlab VXS electronics as an alternative to VME which provides significantly more bandwidth for future experiments that demand this.

# 2. Functional Description

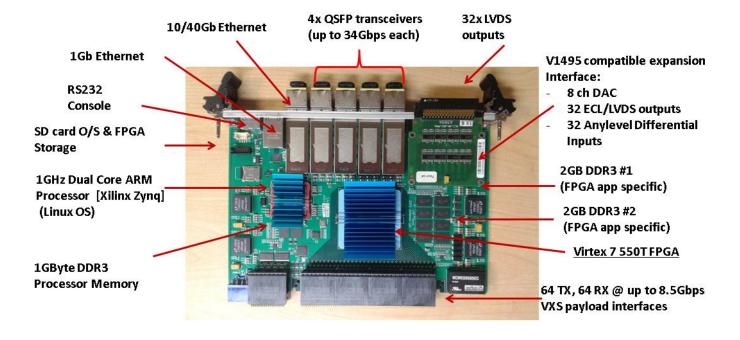

### 2.1 XC7V550T FPGA

The XC7V550T FPGA manages all the VXS backplane and optical serial streams. Custom trigger firmware collects information from the front-end (VXS payload) modules using 4 full duplex SerDes lanes. Up to 4 QSFP front panel ports can be used to communicate trigger information of other front-end crates and to the global trigger crate. LVDS (32) outputs can be used to send fixed latency trigger signals to a TI master for local crate triggering or TS (Trigger Supervisor) for global system triggering. A V1495 compatible mezzanine connector exists that allow use of commercially available ECL/TTL/NIM/ADC/DAC expansion modules mainly to eliminate the need for external level translators. Two DDR3 memories interfaces exists (each with 100Gbps bandwidth) that can be used for large event data buffers in future event building applications, debug/trace buffers, trigger logic dictionaries, histograms, etc. Dual 16bit AXI streaming busses providing a total of 40Gbps connect to the Zynq FPGA which can be used to transport high speed event data to the 10/40Gbps Ethernet. For FPGA configuration and register access a 32bit data slave bus exists which connects to the Zynq FPGA who acts as the bus master.

# **Summary of Features for the XC7V550T**

- 16x VXS payload interfaces: 4 full duplex lanes @ up to 8.5Gbps each

- 4x QSFP interfaces: 4 full duplex lanes @ up to 8.5Gbps each

- 2x DDR3 interfaces: 64bits each @ 1600MT/s

- Dual 16bit AXI streaming bus (up to 40Gbps) transmitter to XC7Z7030

- TRIG1, TRIG2, SYNC from VXS

- 32bit LVDS output (>250Mbps per bit)

- 32bit V1495 daughtercard expansion (A395x)

- Virtex7 FPGA (364000LUT, 692800FF, 5MB BRAM, 2880DSP)

# Summary of Responsibilities for the XC7V550T

- Manage 80SerDes links on the 16 VXS payload and 4 QSFP interfaces

- Run detector/experiment specific level 1 trigger algorithms

- Provide scalers and configuration registers to monitor/manage level 1 trigger

- Receive readout trigger and build experiment specific event data, stream to ROC in ZYNQ

- (Future) receive event data from 16 VXS payload and stream to ROC/EB in/through ZYNQ

### 2.2 XC7Z7030 FPGA

The XC7Z7030 is an FPGA and processor contained in a single chip. The processor is a dual ARM Cortex-A9 which runs Linux and the FPGA provides reasonably large resources to deal with hardware interfaces.

### **Summary of Features for the XC7Z7030**

- Dual ARM Cortex A9 1GHz processor, 1GB DDR3 RAM 32bit @ 1333MT/s

- Bootloader in microSD card

- RS232 Console (115200bps, 8b, np) used for boot configuration and debug terminal

- 10/100/1000Gbps Ethernet used by Linux O/S

- 32bit data/address bus master which memory maps register space of XC7V550T into processor

- 16bit FPGA configuration bus for programming XC7V550T image

- Dual 16bit AXI streaming bus (up to 40Gbps) receiver from XC7V550T

- 10/40Gbps Ethernet intended for FPGA accelerated TCP/IP stack for high speed event building

- 1Gbps TI (PP18) full duplex link

- Kintex7 FPGA (78600LUT, 157200FF, 1MB BRAM, 400DSP)

### Summary of Responsibilities for the ZYNQ Processor/FPGA

- Execute FSBL and U-Boot bootloaders from microSD card, load centrally managed Linux kernel and filesystem from NFS

- Program XC7Z7030 and XC7V550T FPGA images on boot from network

- Runs CODA ROC, event building data from TI and XC7V550T

- Report various scalers, temperatures/voltages to EPICS IOC

- Provides drivers for all VTP peripherals

- (Future) use 10/40Gbps Ethernet to stream event builder data from partial hardware accelerated ROC

# 3.1 Specification & I/O Summary

The VXS connection is used to interface to the trigger system without the need for loose cabling. This interface provides the following signals:

| Signal     | Description                                      | Direction | Signal | Interface |

|------------|--------------------------------------------------|-----------|--------|-----------|

|            |                                                  |           | Type   |           |

| Clock      | 125/250MHz System Synchronous Clock              | In        | LVPECL | SD        |

| Trig1      | L1 accept trigger bit, synchronous to clock      | In        | LVPECL | SD        |

| Trig2      | L1 accept trigger bit, synchronous to clock      | In        | LVPECL | SD        |

| Sync       | L1 synchronization bit, synchronous to clock     | In        | LVPECL | SD        |

| Busy       | Module busy signal                               | Out       | LVDS   | TI        |

| GTP_TX     | 1Gbps VTP->TI TILINK                             | Out       | LVDS   | TI        |

| GTP_RX     | 1Gbps TI->VTP TILINK                             | In        | LVDS   | TI        |

| SDA/SCL    | TI I2C slave interface                           | InOut     | LVTTL  | TI        |

| STATOUT    | Payload->VTP status input                        | In        | LVTTL  | PP1-16    |

| STATIN     | VTP->Payload status output                       | Out       | LVTTL  | PP1-16    |

| L1 Trigger | 8.5Gbps per lane (4) used to generate L1 trigger | In/Out    | CML    | PP1-16    |

# 3.2 Specification Summary

# MECHANICAL

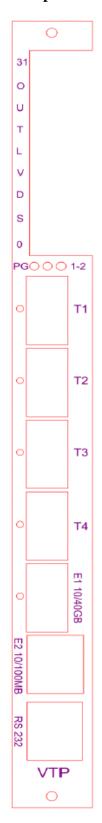

• Single width VITA 41 (VXS) Switch Module

# Trigger Interface and Switch B signaling

# (Signal Distribution module)

- 250MHz Clock (LVPECL)

- Trig1, Trig2, Sync (LVPECL)

- LINKUP out (LVTTL)

- BUSY out (LVTTL)

# **GIGABIT DATA STREAMS**

From/To 16 Payload Slots (FADC, SSP, VETROC, DCRB, etc.)

- 4 full duplex lanes up to 8.5Gbps

- 544Gbps Aggregate

### Outputs:

- 32 LVDS front panel outputs to Trigger Supervisor

- 1x RJ45: 100/1000Mbps Ethernet

- 32 I/O expansion mezzanine (LVDS/ECL/PECL/NIM/Analog)

- 4x QSFP Fiber Transceivers (34Gbps)

- 10/100/1000Mbps Ethernet (RJ45)

- 1x QSFP 10/40Gbps Ethernet

- RS232 console serial port

### Indicators: (Front Panel)

- Power Blue LED

- Trigger Amber LED

- Alarm Red LED Programming and Trigger Data Input:

- On board JTAG Port

- Virtex 7 550T; 80GTH Gigabit transceivers

- 1GHz ZYNQ-7030 SoC processor with Linux OS

- Global Trigger equation and processing for up to 16 JLAB SubSystem Processors

- Front End Trigger processing for up to 16 JLAB Flash ADC digitizers

- 8GB Micro SD card support (Linux OS file system + FPGA image)

- 1GB DDR3 SDRAM

### Power Requirements:

- +5v @ 10 Amps (typ. from Backplane)

- Local regulators for other required voltages

# **Environment:**

- Forced air cooling: Heat sink

- Commercial grade components (85°C max)

# 4. PCB Assembly View

The VTP PCB is a 22-layer impedance controlled FR-408HR stackup

# 5. ARM CPU Configuration

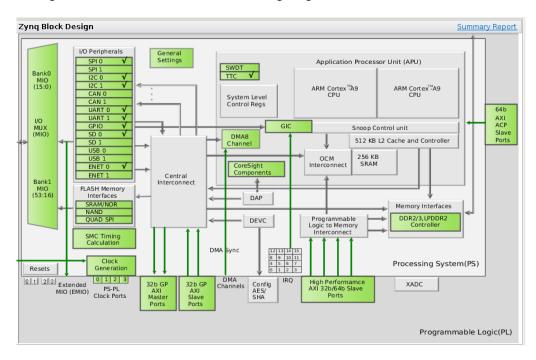

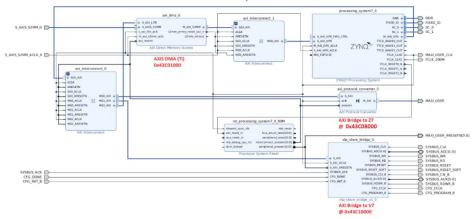

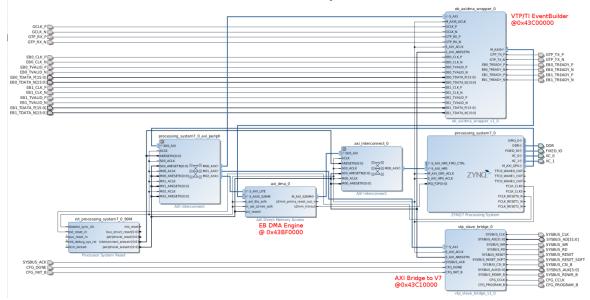

All VTP board registers (whether in Virtex 7 or Zynq 7) are memory mapped into the Zynq7 CPU address space. Many peripherals used in the Zynq7 are part of the PS (Processor System) and the Zynq7 technical reference manual can be referred to for details (ug585-Zynq-7000-TRM.pdf). The Zynq7 processor configuration is summarized in the following diagram:

The following table indicates which PS peripherals are used on the VTP:

# **PS Peripherals:**

| Peripheral Name | Description                                                    | Address Base |

|-----------------|----------------------------------------------------------------|--------------|

| SPI0            | Used by: Si5341 clock synthesizer                              | 0xE0006000   |

| I2C0            | Used by: 10/40Gbps QSFP for module identification & monitoring | 0xE0004000   |

| I2C1            | Used by: LTM4676 smbus power supply monitoring                 | 0xE0005000   |

| UART0           | U-boot & Linux console                                         | 0xE0000000   |

| GPIO            | Used by: Si5341, LEDs, 10/40Gbps QSFP, VXS STAT IN/OUT         | 0xE000A000   |

| SD0             | μSD card is the Zynq7 boot resource (contains FSBL, U-Boot)    | 0xE0100000   |

| ENET0           | 10/100/1000Mbps Ethernet for U-Boot & Linux                    | 0xE000B000   |

| TTC0            | U-Boot & Linux OS Timer                                        | 0xF8001000   |

# 6. Streaming Readout

The VTP was developed as a trigger processor, but the high bandwidth serial connections to the VXS backplane modules as well as optical outputs has provided an opportunity to convert to a streaming DAQ architecture (avoiding the need for the trigger data/processing path).

# **FADC250 Streaming Firmware**

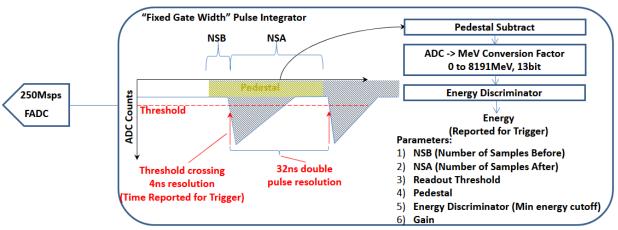

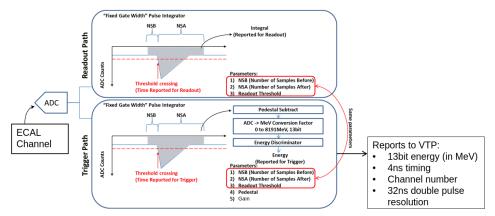

The first streaming DAQ implementation with the VTP and FADC250 used the FADC trigger output as the streaming data source. The trigger output of the FADC250 uses the VXS P0 interface to streaming FADC hits over a 10Gbps interface (4 lanes at 2.5Gbps, 8b10b encoded provides 8Gbps of usable bandwidth). The 8Gbps usable bandwidth was sufficient to allow a simple reporting scheme that allows each channel of the FADC250 to report a 13bit charge and 4ns timestamp pulse hit with a 32ns double pulse resolution (e.g. 16ch \* (13bit charge + 3bit fine

time) / 32ns = 8Gbps). The FADC250 uses a programmable threshold to detect a leading edge of pulses. When the leading edge is found, a programmable number of samples before, NSB, and after, NSA, are summed together to form the pulse integral. A pedestal is subtracted from the integral and a gain is applied to convert the value into the desired units (typical examples: 1MeV, 100keV, Npe). The resulting value is capped to 8191 so that it fits into the 13bit charge field that is reported to the VTP – if the value exceeds 8191 the FADC will report 8191 (so this capped value can be used as an overflow detection if desired). The following figure illustrates this pulse processing logic:

The FADC250 data format can change easily in the future with firmware updates. Plans are already made to change the trigger output to report more information (to more closely match the information it typically reports in VME readout mode), such as time walk corrected timestamping with much higher resolution as well as raw waveform samples. This additional information will reduce the hit rate capability of the streaming system, but the bandwidth is significant this limit will still be extremely high for most detector channels used in experiments at Jlab.

# **VTP Streaming Firmware**

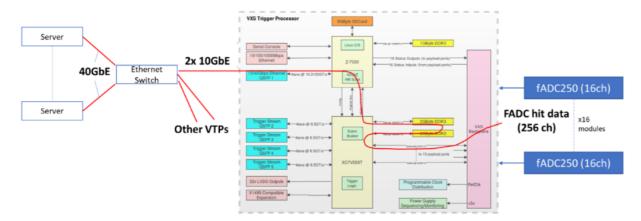

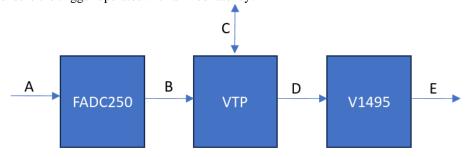

The following image shows the path of the streaming data through the hardware:

### **FADC Input**

FADC250 data is received at 10Gbps (8Gbps of useful data) from each of the 16 payload slots. Data from each FADC250 is buffered into DDR3 memory where each modules has 256MBytes of buffering. This buffer is used to allow significant burst of occupancy and/or handle significant downstream network delays without loosing any data. If high occupancy persists for too long that exceeds the network bandwidth then data will be dropped by the VTP and details on this will be discussed below.

# **FADC/VTP Streaming Data Path**

Currently, the VTP streaming firmware implements 2 parallel instances of the FADC250 streaming system. Each instance handles 8 slots of FADC250, and has a dedicated 2GByte DDR3 buffer and 10Gbps Ethernet link. A future plan is to make 4 parallel instances in the firmware so that the all 4 lanes of the QSFP are usable for streaming each at 10Gbps (an additional 16 optical links can be used as well, but are limited to 8.5Gbps or if the speed grade of the FPGA is increased then 10Gbps is also achievable). Ethernet was chosen for the streaming readout interface because of its widespread support/compatibility. It is easy to buy additional commercial switches to scale the network as needed. We also already have significant amounts of VTP and VXS crates on site at Jlab, so we can take advantage of the available resources and run standard TCP/IP on the ethernet link to ensure simple and reliable data transfer to nearly any PC.

### **TCP/IP Interface**

The VTP is programmed with the destination IP address and socket for where the 8 FADC slots of streaming data are sent. We can consider supporting additional destinations/sockets if needed to distribute a lesser load to servers, but as computing power is increasing it does appear that a single socket/server per 10Gbps is feasible for data transfers. A hardware accelerated TCP/IP stack implemented in VHDL is used to achieve deterministic and and throughput on the network. The TCP transmit buffer is limited to 64kBytes and have been able to achieve ~8Gbps throughput when streaming to Linux based servers.

# **Data formatting**

Data is built into a TCP data frames that contain a header (containing frame number, timestamps, and other information helpful in ensuring data coherency and timing synchronization) and a payload (the customizable information by the streaming DAQ, currently the FADC hit data). The TCP frames correspond to a programmable span of time, typically 65536ns, for which the reported FADC hits have been collected. When the DAQ starts, the VTP modules also synchronously start their timers that are used to timestamp FADC hits. Each time a frame time has elapsed a TCP data frame is sent containing the hits for that time span. The 'C' structure for the data frame is as follows:

```

typedef struct stream_buffer

{

uint32_t source_id;

uint32_t total_length;

uint32_t payload_length;

uint32_t compressed_length;

uint32_t magic;

uint32_t format_version;

uint32_t flags;

uint64_t record_counter;

struct timespec timestamp;

uint32_t payload[];

} stream_buffer_t;

```

**source\_id:** definable by software on each VTP, intended as a unique identifier **total\_length:** length (in bytes) of stream\_buffer\_t (including variable length payload, and excluding source\_id)

payload\_length: length (in bytes) of payload[] element. Can be zero.

compressed\_length: not used, and currently set to payload\_length

magic: should always be set to 0xC0DA2019

**format\_version:** used to specify version of this data format (no official versions have been released yet, so kind of meaningless for now)

flags: no flags have been defined, meaningless for now

payload: variable length (0 to payload\_length/4-1), front-end defined readout data

Main features are the timestamp (a 1ns resolution absolute timestamp for the FADC hit data frame). This timestamp should be added to the local timestamps of the FADC data hits. The record\_counter indicates the frame number and will be received sequentially – if a frame is dropped due to overflowing data the record\_counter will show a jump/gap.

The payload[] data should be parsed by looking for a data type (indicated by bit31=1 and type in the bits 30:15). The data type indicates the data to follow. The payload[] element contains the variable length streaming data (e.g. FADC hits). In addition to the FADC hits (data type = 1) there exists an FADC hit pointer structure (data type = 0) that is used to allow the receiving software to know where each FADC slot data exists in the payload and how long it is – the eliminates the need for the receiving end to parse the full payload before distributing parts to different processes.

```

The FADC pointer structure is as shown below.

typedef struct fadc_ptr

{

uint32_t type; // set to 0x80000000, bits 30:15=0 (FADC pointer type)

uint32_t ptr_len[8];

} fadc_ptr_t;

```

The array of 8 ptr\_len elements correspond to the 8 FADC slots reported on this streaming socket. The 32bit ptr\_len contains the offset for the data in payload[] in bits 15:0, and the length is contained in bits 30:16.

```

The FADC hit structure is as shown below.

typedef struct fadc_hit

{

uint32_t type;

uint32_t hit[];

} fadc_hit_t;

```

FADC hit type will have the bit assignment: 31=1, bits 30:15=1 (FADC Hit type), 14:8=roc\_id, 4:0=fadc slot number. Then a variable number FADC hits will follow and have the following format: bit 31=0, bit 30:17=4ns timestamp, 16:13=channel, 12:0=charge

### **Data loss handling**

For the moment the VTP is responsible for dropping streaming data when downstream pipes can't accept a higher input rate for long periods of time. Burst conditions (on the order of ~100msec at 32MHz/channel for all channels) are handled without data loss by the VTP DDR3 memory buffers. When the buffers are full, entire frames (e.g. 65536ns chunks of data) are dropped. These losses should not happen under normal conditions when the network and processing are sufficient

to keep up with the readout data (or if thresholds are too low) - the record\_counter in the CODA SRO header can be used to identify dropped data.

# 7. VTP CODA Software ROC

# 7.1 Description

The VTP Zynq ARM processor is capable of running the traditional CODA ROC software components. The reason the VTP needs a ROC is mostly for diagnostic event data recording. The VTP performs trigger processing in many applications where some involve making complex decisions where the efficiency & correctness of these decisions needs continuous verification and monitoring throughout experiments. The software ROC is capable of running over 70kHz with event blocking and minimal deadtime. The VTP receives TI event block data using a proprietary 1Gbps serial link. This same serial link provides information on the event blocking level, sync event status, and block acknowledgement. TI and VTP generated event data can be read using single 32bit reads over the AXI bus, or use the AXIS DMA engine to achieve high performance. Readout is sent to the CODA event builder using the Linux OS controlled 1Gbps Ethernet link.

### 8. VTP CODA hardware accelerated ROC

### 8.1 Description

The VTP has a serial link to each VXS payload module primarily used for trigger data, but the link speeds are programmable and offer additional bandwidth that can be utilized as an alternate path for event data readout (instead of using the VME bus). The CODA ROC runs partially in software (initialization, asynchronous event injection, and low data rate synchronous event generation), while the large bandwidth event building and transport to the CODA EB are done using the FPGA (including a fully firmware based 10Gbps TCP/IP Ethernet solution).

# The primary benefits are:

- 1) payload modules can be readout in parallel (where on VME they were readout sequentially)

- 2) readout bandwidth from payload modules to the VTP is guaranteed and not shared

- 3) the VTP readout bandwidth to the CODA event builder is close to 10Gbps (and upgradable to 40Gbps in a future firmware)

- 4) setups that already have a VTP installed for triggering purposes can receive this accelerated readout option is basically at no cost (for setups without a VTP, the cost is only the VTP which is often much cheaper than replacing the full front-end hardware)

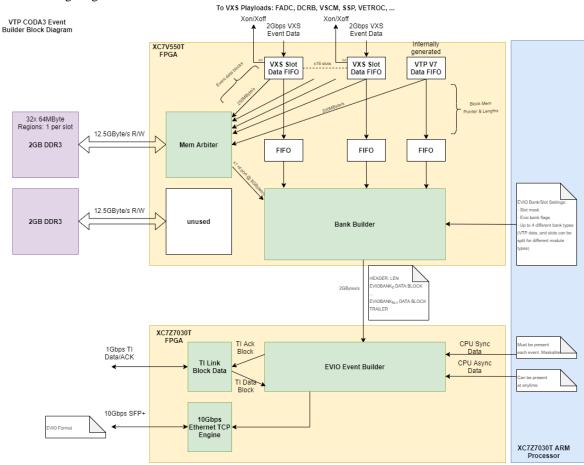

The following diagram illustrates the hardware/firmware resources used:

Serialized event data will be separated from the trigger input streams and buffered into one of the 2GByte DDR3 memories. The bandwidth of this memory is ~10GByte/s so is plenty capable of sustaining the traffic to saturate the 10Gbps Ethernet link. Future implementations can take advantage of multiple 10Gbps links or possibly use a single 40Gbps Ethernet link. Event data from the payload modules are buffered into

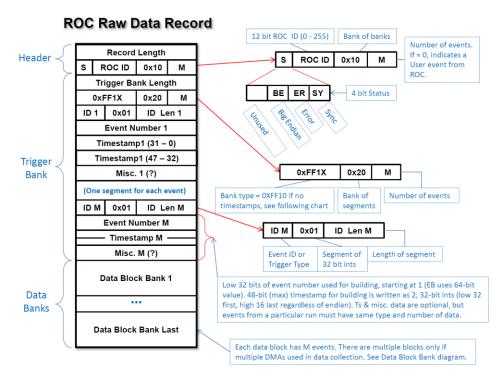

the DDR3 memory. The Virtex 7 FPGA can arrange the payload module data from each module to be assembled into 1 of 3 definable EVIO banks. All 16 payload modules can go into a single EVIO bank, or they can be split up into any of the 3 banks. This is useful in the case where multiple different module types exist in the crate and if it is desired their data lives in different EVIO banks. The Virtex 7 builds a single EVIO bank and computes the length, which contains up to 3 EVIO banks containing the payload data (so we're builing an EVIO bank of banks). The structure used is as follows, with type = 0x10 for the main EVIO bank, and the 1 to 3 banks inside use type = 0x1 for 32bit unsigned types):

# Bank: MSB (31) Length (32 bit words, exclusive) Tag (16 bits) Padding Num (8) Number of unused bytes at end of following data if not a multiple of 32 bits. For shorts, it is 0 or 2. For chars (not strings), it is 0, 1, 2, or 3

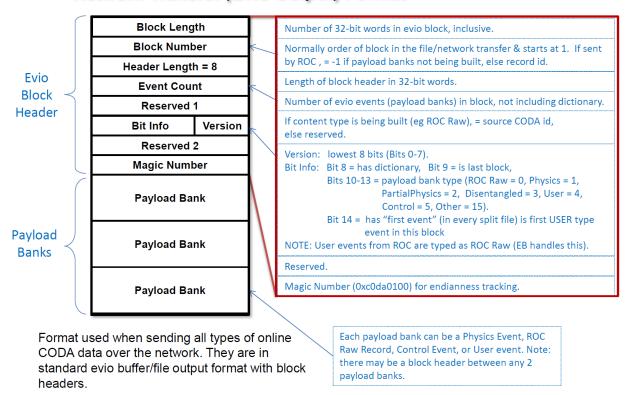

This Virtex 7 EVIO bank header information is presented to the Zynq 7 FPGA where the final EVIO structure is built intended to communicate directly with CODA event builders. This final format adheres to the following structure:

# **Network Transfer (Evio Output) Format**

The Zynq 7 FPGA will assemble the Payload Bank which contains the TI block data, and optionally an ARM CPU generated Data Block, and the Virtex 7 Data Block following this format:

The VTP HW CODA ROC will only build physics events in firmware. CODA control events that are not physics events must use the VTP ARM Processor asynchronous event data interface. This asynchronous interface can be used to generate the required control events at the beginning and end of runs (but it can also be used to send asynchronous event data in the middle of ongoing runs for things like scalers, config data, or whatever else may be useful to record).

### 8.2 ARM CPU Peripheral Configuration

The ARM CPU/FPGA peripherals are as follows (and will be made standard on all VTP CODA ROC firmware versions):

- 1) AXIS DMA (TI): allows DMA transfer of TI event blocks into ARM system memory https://www.xilinx.com/support/documentation/ip\_documentation/axi\_dma/v7\_1/pg021\_axi\_dma.pdf

- 2) AXI Bridge to Z7: allows CPU AXI-lite transactions to Zynq FPGA peripherals

- 3) AXI Bridge to V7: allows CPU AXI-line transactions to Virtex 7 FPGA peripherals (and also the same bus used to load the Virtex 7 FPGA firmware)

# 8.3 Zynq 7 FPGA Peripheral Configuration

Zynq 7 FPGA peripherals exist on the "AXI Bridge to Z7" component. The peripheral address offsets are described here (and are relative to the "AXI Bridge to Z7"):

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_z7/vtp\_z7\_pkg.vhd

Peripherals used on the VTP CODA ROC are as follows (and will be made standard on all VTP CODA ROC firmware versions):

### PER ID TI

1Gbps link between VTP and TI used to transfer block of TI event data and control/acknowledge signals between these modules.

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_z7/z7\_ti\_per/z7\_ti\_per.vhd

# PER\_ID\_CLK

Z7 FPGA clocks, resets, firmware version & timestamp.

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_z7/z7clk\_per/z7clk\_per.yhd

### PER ID CODA ROC

HW CODA ROC, also allows asynchronous and synchronous event data injection.

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_vxs\_readout\_z7/coda\_roc\_per/coda\_roc\_per.vhd

### PER\_ID\_10GBE\_TCPIP\_CLIENT0

HW 10Gbps TCP/IP Ethernet stack. The VTP CODA ROC uses this interface as a TCP client (e.g. it makes the connection to the TCP server)

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_z7/z7\_10GbE\_tcpip\_per/z7\_10GbE\_tcpip\_per.vhd

### PER ID EBIORX0

V7->Z7 16Gbps data bus receiver where the V7 FPGA CODA EVIO bank is received (which contains data from the VXS payload modules)

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_vxs\_readout\_z7/ebio\_rx\_per/ebio\_rx\_per.vhd

### 8.4 Virtex 7 FPGA Peripheral Configuration for FADC readout

Virtex 7 FPGA peripherals exist on the "AXI Bridge to V7" component. The peripheral address offsets are described here (and are relative to the "AXI Bridge to V7"):

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_v7/vtp\_v7\_pkg.vhd

### PER ID CLK

V7 FPGA clocks, resets, firmware version & timestamp.

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_v7/v7clk\_per/v7clk\_per.vhd

### PER ID QSFP0..3

OSFP transceiver and data links

$\underline{https://github.com/JeffersonLab/fe} \ \underline{fw/blob/devel/Firmware/Source/vtp. v7/v7aurora8b10b. per/v7aurora8b10b. per/v7auror$

### PER ID VXS0..15

VXS transceiver data links. Actual payload ID is +1 to the peripheral index.

$\underline{https://github.com/JeffersonLab/fe\ fw/blob/devel/Firmware/Source/vtp\ v7/v7aurora8b10b\ frm\ per/v7aurora8b10b\ per/v7aurora8b10b\ frm\ per/v7aurora8b10b\ frm\ per/v7aurora8b10b\ frm\ per/v7aurora8b10b\ frm\ per/v7aurora8b10b\ frm\ per/v7aur$

# PER\_ID\_SD

Signal distribution management peripheral.

$\underline{https://github.com/JeffersonLab/fe} \ \, \underline{fw/blob/devel/Firmware/Source/vtp} \ \, \underline{v7/v7sd} \ \, \underline{per/v7sd} \ \, \underline{per$

# PER\_ID\_EVT\_BUILDER

V7 payload module EVIO bank configuration

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_vxs\_readout\_v7/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per.vh

### PER\_ID\_MIGPER\_R

V7 DDR3 memory configuration

https://github.com/JeffersonLab/fe fw/blob/devel/Firmware/Source/vtp v7/v7mig per/v7mig per.vhd

### PER\_ID\_EBIO\_TX0

V7->Z7 16Gbps data bus transmitter where the V7 FPGA CODA EVIO bank is received (which contains data from the VXS payload modules)

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_vxs\_readout\_v7/ebio\_per/ebio\_tx\_per.vhd

### 8.5 Virtex 7 FPGA Peripheral Configuration for MPD readout

MPD readout is very similar to the standard FADC readout except that each payload port may have up to 4 MPD connections. Currently only 32 MPD may be readout using VME slots 3-10 (this may be expanded in the future if needed). The MPD also has a unique processing block to perform zero suppression, common-mode subtraction, and remote register access so that MPD readout will be done using a dedicated V7 FPGA image/type. Virtex 7 FPGA peripherals exist on the "AXI Bridge to V7" component. The peripheral address offsets are described here (and are relative to the "AXI Bridge to V7"):

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_v7/vtp\_v7\_pkg.vhd

### PER ID CLK

V7 FPGA clocks, resets, firmware version & timestamp.

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_v7/v7clk\_per/v7clk\_per.vhd

### PER ID MPDFIBER0..31

MPD fiber control and processing interface. Fiber 0,1,2,3 correspond to the serial lanes VME slot 3. Fiber 4,5,6,7 correspond to the serial lanes of VME slot 4, etc. The VME slots are requires to have a VXS to QSFP payload module that converts the serial link to optics that interface the MPD.

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_mpd\_readout\_v7/mpd\_fiber\_per/mpd\_fiber\_per.vhd

### PER ID MPDREGS

This peripheral is used to access registers on the remote MPD.

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_mpd\_readout\_v7/mpd\_register\_per/mpd\_register\_per.vhd

### PER ID SD

Signal distribution management peripheral.

https://github.com/JeffersonLab/fe fw/blob/devel/Firmware/Source/vtp v7/v7sd per/v7sd per.vhd

# PER\_ID\_EVT\_BUILDER

V7 payload module EVIO bank configuration

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_vxs\_readout\_v7/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vtp\_evt\_builder\_per/vt

9

# PER\_ID\_MIGPER\_R

V7 DDR3 memory configuration

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_v7/v7mig\_per/v7mig\_per.vhd

### PER ID EBIO TX0

V7->Z7 16Gbps data bus transmitter where the V7 FPGA CODA EVIO bank is received (which contains data from the VXS payload modules)

https://github.com/JeffersonLab/fe\_fw/blob/devel/Firmware/Source/vtp\_vxs\_readout\_v7/ebio\_per/ebio\_tx\_per.vhd

# 9. NPS Cluster Trigger

# 9.1 Description

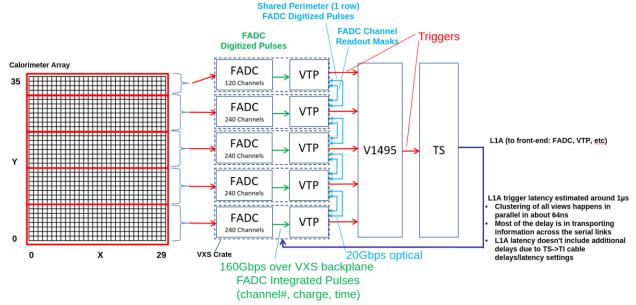

The NPS calorimeter is comprised of an array of 30x36 PbWO<sub>4</sub> blocks with a PMT and analog amplifier for each block. The amplifiers connect to the Jlab FADC250 modules for creating a trigger and readout. The purpose of the NPS cluster trigger is to find clusters in the calorimeter with high efficiency and minimal bias. When a cluster is found over threshold a trigger signal will be sent to the counting where it can trigger the DAQ directly or be used in coincidence with other detectors.

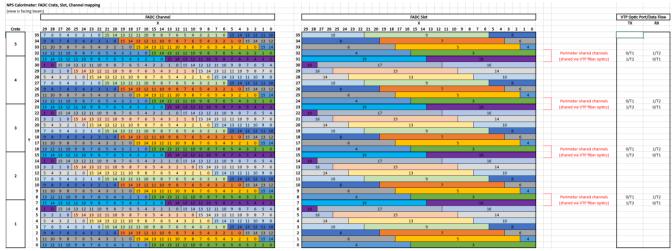

The segmentation of the calorimeter into VXS crates & FADCs was done such that each crate looked the same: same number of channels and the local mapping/view of the calorimeter was the same. This allows the clustering firmware in the VTP to be the same in all crates and only a Y coordinate offset is needed to distinguish each crate. The top of the calorimeter also works this way even though it has fewer channels. The following figure illustrates the segmentation and DAQ connections:

Another requirement of the NPS cluster trigger is to support sparsification of the FADC250 readout channels and only readout FADC channels centered on found clusters. This allows the FADC250 readout to report the full raw waveforms for event data, which is data volume intensive, but the sparsification will reduce the number of reporting channels from 1080 to a much smaller fraction. This significantly reduces the data volume and at the same time allows readout of waveforms for very small signals around the cluster center without having to apply an individual channel threshold online.

# 9.2 Trigger data flow

### 9.2.1 FADC pulse detection

The trigger processing begins in the FADC250 with identifying and measuring the total charge of individual pulses on each channel. A software configurable threshold, **FADC250\_TET**, which sets a common threshold for one or more FADC250 modules. These units are in FADC units: for NPS the FADC250 are in 1V dynamic range mode, so each FADC sample unit is  $1V/4096 = 244\mu V$ . The threshold is relative to the software defined pedestal, **FADC250\_ALLCH\_PED**, which is a floating-point number specifying how many FADC units should be removed from each sample when performing a pulse integral. When the FADC input samples see a threshold crossing (previous sample <= PED+TET, next sample > TET) the pulse sum is formed around the threshold crossing: NSB (number of samples before the threshold crossing) and NSA (number of samples after the threshold crossing) samples are summed to compute the pulse integral. Next the pedestal is subtracted, and the gain is applied. The resulting pulse integral can be summarized by (where Sample[] is the array of FADC samples and N is the sample where the threshold crossing occurs):

$$PulseIntegral = GAIN \cdot \sum_{n=N-NSB}^{N+NSA-1} (Sample(n) - PED)$$

Integrated pulses can overlap, the requirements needed to ensure a pulse integration occurs is:

- 1. A threshold crossing is seen

- 2. No threshold crossing occurred in the past 7 clock cycles (last 28ns)

The second requirement is needed to ensure no more than 1 pulse every 32ns can be reported (this is a bandwidth limit on the communication link from FADC -> VTP). It also helps to suppress multiple threshold crossings due to pulse ringing or noise. This also means the FADC trigger path can miss a legitimate pulse if too close to a previous one. The pulse integration is summarized by the lower "Trigger Path" part of the following figure:

The resulting pulse integral must also be constrained to 13bits due to bandwidth limitations. So it is important that the FADC GAIN parameter is set so that the desired pulse integral dynamic range is scaled to fit in the 0 to 8191 range set by the 13bit limitation. Normally the GAIN is setup such that the resulting gained integral units are in MeV. After applying the gain, any values less than 0 saturate at 0 and any values greater than 8191 saturates at 8191.

### 9.2.2 Streaming FADC hits to VTP

Each FADC250 communicates with the VTP using 4 full duplex dedicated links per FADC250. Each link runs at 3.125Gbps with 8b10b encoding. This results in 10Gbps of bandwidth available between each FADC250 to the VTP. The Xilinx Aurora framing protocol is used as a lightweight interface, which defines all the necessary control characters, synchronization, lane-bonding, and framing parameters to make it easy to develop on top of. The FADC sees a 64bit data path running at 156.25MHz and it must fit 31.25MHz \* 16 channels \* 16bits of pulse integral/timing information. The necessary bandwidth for this trigger path is 8Gbps, where the FADC can effectively send 13bit energy, 3bit timestamp for 16 channels every 32ns. The 3bit timestamp is needed to identify the pulse time to 4ns resolution within the 32ns window the data is sent. The VTP receives this stream and decodes it such it sees FADC channel pulse integrals for all 256 channels with 4ns timing resolution – the generic basis from which a variety of applications can take this data to build custom algorithms.

Clustering also has to work seamlessly across the VXS crate boundaries. To do this the FADC pulses are the crate borders are exchanged with the adjacent crate. The segmentation of the calorimeter channels was done to ensure the bordering channels were able to fit on a single VTP fiber link (which runs at 20Gbps 8b10b, so 16Gbps usable – exactly enough to send 32 FADC channels over 1 link). These links are bi-directional so a crate sending FADC pulses to the adjacent crate will also receive from that crate so that same crate. The FADC250 channel/slot map is shown along with the channels shared and what VTP fibers are used to do that (shown all the way on the right):

As mentioned before the firmware for each of the VTPs is the same so that locally they see the same channel map (the only parameter the VTPs need set is the unique Y offset set by software). It is as follows:

The final resulting FADC pulse stream seen by each VTP consist of the local FADC250 pulses reported over the VXS backplane and the remote FADC250 pulses received over fiber shared from adjacent VTPs. The data from these different sources show up at different times due to different path delays. To remove this skew, the VTP is configured to know which FADC and Fiber ports are active for the trigger processing. Once the TS releases SYNC, the FADC250 stream integrated pulses to the VTPs, the latency is around 300ns for a small NSA parameter (e.g. NSA ~36ns). The VTP forwards certain FADC channels over fiber to the adjacent VTPs. The FADC pulses are all stored in a FIFO that are not read until all enabled FADC and fiber sources have data ready. Once all FIFOs have data ready the VTP can begin reading and this provides the full FADC pulse information that is aligned in time that the trigger logic can begin to process. The overall latency of this is about 1800ns (time for data from FADC to be read by VTP trigger logic that is aligned in time across all slots & fibers).

### 9.3 Clustering logic

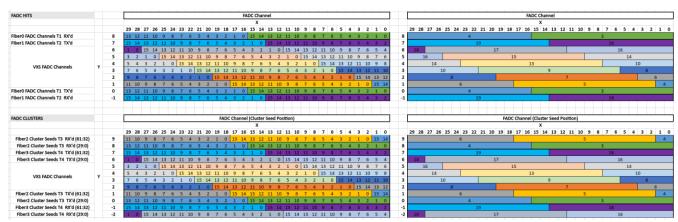

Clustering is performed on FADC pulses in both space and time using all possible overlapping 3x3 views of the calorimeter. This results in 1080 possible views and is how many cluster processing units running in parallel to quickly perform this task (in about 96ns). A single cluster processing unit needs to see only the 3x3 view of FADC channels it will cluster. Within the cluster processor, a cluster will be found/formed using the following rules:

- a. Central block has energy >= software defined cluster seed threshold defined by the config

VTP NPS ECALCLUSTER SEED THR

- b. Central block energy is >= all immediate surrounding block energies in 3x3 view (i.e. it is a local maximum) that are withing the timing coincidence window defined by

VTP NPS ECALCLUSTER HIT DT

- c. The cluster sum is formed by adding up the pulse energy of the central crystal along with the largest pulse energy in the timing coincidence window (defined by VTP\_NPS\_ECALCLUSTER\_HIT\_DT) from each of the 8 channels surrounding the central block

d. The cluster seed position is the reported (X,Y) position and time of the cluster, along with the cluster sum, and the number of channels that had a hit in the 3x3 window

The following figure shows a single 3x3 cluster processor view and the cluster it forms given a seed threshold of 2 and hit  $dt = \pm 8ns$

Finding clusters in both space and time prevent multiple clusters from being found from adjacent 3x3 views so that 1 cluster is reported for each physical cluster in the calorimeter (exceptions to this can be if the channels have poorly calibrated gains, thresholds, pedestals, timing offsets, noise, and/or cable reflections).

All of these found clusters are send to various trigger processing stages (cluster singles and cluster pair processing). These clusters are stored in an 8µs, similar to FADC samples, so that when the system is triggered the VTP will record all found clusters in its readout window (useful for verification and monitoring clusters that the FADC may not readout due to sparisfication cuts).

### 9.4 Trigger Types

The following sections will describe the conditions needed to meet the trigger bit requirements that generate the VTP trigger bit pulses. See section "VTP Trigger Bits & V1495 Trigger Bits" for trigger bit mapping details.

### 9.4.1 Cluster singles trigger

Cluster singles trigger is the primary NPS production data trigger. The conditions to create a trigger are as follows (where a single cluster must satisfy all conditions):

Cluster.Energy >= VTP\_NPS\_ECALCLUSTER\_CLUSTER\_TRIGGER\_THR

Cluster.NHits >= VTP\_NPS\_ECALCLUSTER\_NHIT\_MIN

When the condition is satisfied the trigger time is a based on the Cluster. Time, which is the central hit/seed hit time. It is delayed by the software programmed trigger latency parameter:

VTP\_NPS\_TRIG\_LATENCY

### 9.4.2 Cluster pair trigger

The cluster pair trigger was requested and added late in the design and the original architecture wasn't setup for a global multiplicity or pair processing (e.g. cluster sum cuts). Individual clusters must meet the following condition (note it shares the same config parameter for NHits cut, but a unique on for the cluster threshold):

Cluster.Energy >= VTP\_NPS\_ECALCLUSTER\_CLUSTER\_PAIR\_TRIGGER\_THR

Cluster.NHits >= VTP\_NPS\_ECALCLUSTER\_NHIT\_MIN

# Local PAIR1 trigger logic

Cluster that past the above conditions will generate a "PAIR1" trigger pulse trigger bit – this trigger signal there is at least 1 cluster in the local crate that satisfies the pair cluster condition. The V1495 will generate a PAIR trigger if it finds 2 or more VTPs with a "PAIR1" trigger asserted at the same time. The coincidence width the V1495 sees for PAIR1 trigger bit inputs is defined by the VTP trigger bit pulse width **VTP\_NPS\_TRIG\_WIDTH**. The V1495 will generate a 100ns trigger pulse to send to the trigger supervisor (when two or more PAIR1 VTP trigger bits are asserted).

### Local PAIR2 trigger logic

A separate trigger bit PAIR2 is generated by each VTP that is asserted when two or more clusters are found in the local crate that both satisfy the above Cluster.Nhits and Cluster.Energy cuts used for the pair trigger. The coincidence window is programmable by the parameter

VTP\_NPS\_ECALCLUSTER\_CLUSTER\_PAIR\_TRIGGER\_WIDTH. The trigger bit is sent to the V1495 using the trigger bit pulse width define by VTP\_NPS\_TRIG\_WIDTH. The V1495 OR's all PAIR2 trigger bits from the VTPs together and this is sent to the trigger superviser.

Note: the pairs found in the V1495 generate a trigger pulse on the same output that the PAIR2 triggers are OR'd onto. So only one pair trigger bit is provided to the counting house trigger supervisor.

# 9.4.3 Cosmic trigger - scintillator

There are 4 scintillator bars connected to nps-vme3 FADC250 slot 20:

Scintillator top bar 0: FADC slot 20, channel 0 Scintillator top bar 1: FADC slot 20, channel 1 Scintillator bottom bar 0: FADC slot 20, channel 2 Scintillator bottom bar 1: FADC slot 20, channel 3

The cosmic trigger will trigger when any hit in either top scintillator is in timing coincidence with any hit in either bottom scintillator. The trigger time will be timed with respect to when both top and bottom are seen in coincidence. The coincidence time is programmable and determines the coincidence time, VTP\_NPS\_COSMIC\_SCINT\_DT. A hit on any of these scintillator channels is defined as any FADC250 threshold crossing on the scintillator that has a non-zero integrated energy (integration by FADC250 NSB & NSA, pedestal subtraction, and gain applied => pulse energy).

### 9.4.4 Cosmic trigger – calorimeter column

This calorimeter column trigger is satisfied by any NPS VTP when it sees FADC channels in a single column of its crate meet the software defined multiplicity in the timing coincidence window. The VTP doesn't apply any threshold cuts, but it does require a non-zero pulse that has crossed the FADC250 channel threshold to see a channel hit. Within each crate, a column is only 8 crystals tall. The multiplicity can be changed from 1 to 8 so conditions can be relaxed if inefficiencies are expected. In addition, there is a veto option that will reject any column trigger if a hit exists anywhere else in another column of the same crate – this is very helpful at rejecting corner clipping tracks. The V1495 can be setup to OR the crates or AND them. When enabling the veto and performing a crate AND at the V1495 almost all events are vertical tracks constrained to a single column of the whole calorimeter – so the event rate is low and purity very high.

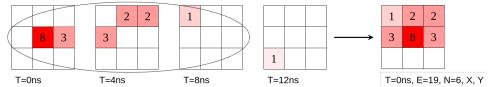

FADC event examples (FADC channels with hits in event. A low threshold often causes channel to see multiple hits) from the testing in EEL with a 3 crate setup (high multiplicity, veto enabled, v1495 AND mode – column shifts may be seen at Y = multiple of 8 boundaries):

The VLD trigger is used for LED trigger runs. The VLD modules have their trigger outputs all OR'd together in a daisy-chained connection with the last module being used as the trigger source for the VLD system. It connects to nps-vme3, FADC250 slot 20 (a spare FADC not used by NPS calorimeter), channel 15. Using the FADC250 as the trigger input allows the latency to closely match the NPS cluster trigger. This trigger is simple as it generates a trigger anytime a leading edge is seen on the FADC input. See section "VTP Trigger Bits & V1495 Trigger Bits" for trigger bit mapping details.

### 9.5 Sparisfication

NPS calorimeter sparsification was done to significantly reduce the data rate while simultaneously supplying raw waveform readout for channels around the cluster (so no individual channel threshold is needed to readout the FADC channels of the cluster, potentially improving offline reconstruction resolution). Either a 5x5 or 7x7 channel pattern centered on the trigger cluster seed is used to determine which FADC channels to readout. The VTP uses another cluster energy threshold to determine what clusters will allow FADC channels to be readout:

VTP\_NPS\_ECALCLUSTER\_CLUSTER\_READOUT\_THR. When the DAQ issues a trigger, the VTP looks back in time to find clusters >= VTP\_NPS\_ECALCLUSTER\_CLUSTER\_CLUSTER\_READOUT\_THR (a lookback time and window width is used so that trigger latency and jitter can be compensated for). Any clusters satisfying the readout cluster threshold will result in a 5x5 or 7x7 FADC channel pattern (selectable by software configuration) to be readout centered on the seed/central block of the clusters. The VTP sends the readout channels masks to all FADCs so they know which channels to keep and throw away data for on each event.

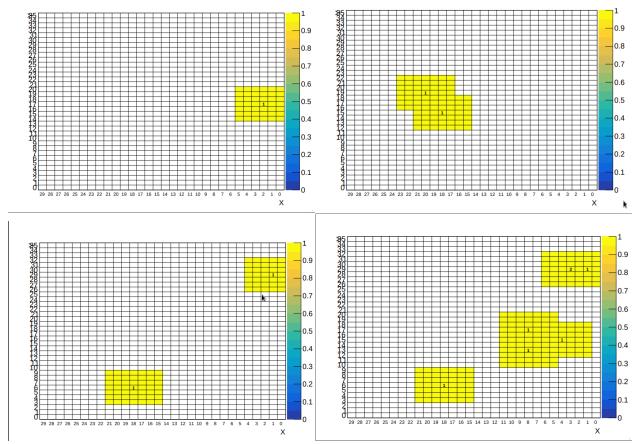

Some examples of this sparsified cluster readout can be shown by the following tests. The pictures show the calorimeter channel layout with yellow blocks indicating the FADC channels the readout sees raw waveforms for and the numbers show where and how many clusters the VTP found at that cluster center position. You can see a variety of examples showing 7x7 readout patterns for separate and overlapping cluster events:

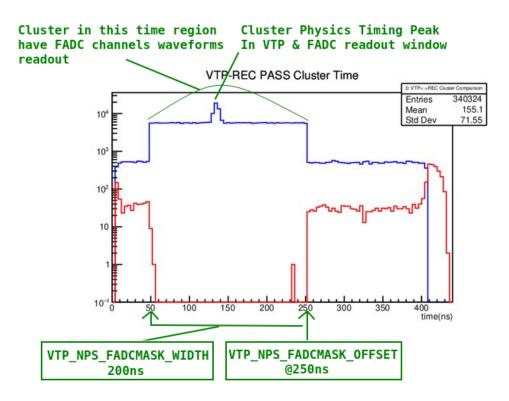

A critically important detail is the timing diagram that illustrates the parameters to setup to ensure a trigger can properly be timed in to capture the VTP clusters to determine these channels patterns. The two main parameters to adjust this timing is the VTP NPS FADCMASK WIDTH and VTP NPS FADCMASK OFFSET. These

parameters decide which time range in the VTP readout window will be looked at to determine which clusters satisfy the readout cluster threshold. The "OFFSET" parameter determines at what point in time of the readout window the VTP will evaluate what clusters are evaluated – the example image below shows this offset at 250ns in the readout window (look at the blue curve, which is the FADC reconstructed cluster trigger times). Then the "WIDTH" parameter determines how much time before and up to the "OFFSET" the VTP will also look for clusters over the readout threshold – the example shows a width of 200ns. In this example you can see we consider clusters from 50ns to 250ns in the readout window, centered with plenty of margin around the physics peak at 150ns. When we readout the FADC channel, we readout the full waveform for the entire (which spans 400ns in the example) - this is why we also see a suppressed background outside the 50ns to 250ns range.

### 9.6 VTP Trigger bits & V1495 Trigger Bits

Each VTP outputs its trigger bits on the front panel ribbon cable (LVDS signals) and they are mapped as follows:

VTP Trigger Bit 0: Cluster Singles

VTP Trigger Bit 1: Cosmic Scintillator

VTP Trigger Bit 2: Cosmic Column

VTP Trigger Bit 3: Pair 1

VTP Trigger Bit 4: Pair 2

VTP Trigger Bit 5: VLD

# **9.6.1 Latency**

The latency of these triggers (roughly the time from an input at the FADC250 to where the VTP produces an output on its trigger bit output) is defined by the programmable parameter:

# VTP\_NPS\_TRIG\_LATENCY

This latency must be at least as long as the total trigger path processing time to ensure deterministic behavior (as of the beginning of NPS runs, it has needed to be least 2.3µs). This parameter can be adjusted to bring it into coincidence with other detectors, but each trigger bit can be individually delayed with the following parameter: **VTP\_NPS\_TRIG\_DELAY**.

### 9.6.2 Prescaling

Trigger bits can also be prescaled with the following parameter: VTP\_NPS\_TRIG\_PRESCALE

### 9.6.3 Trigger width

A programmable trigger bit pulse width (common to all trigger bits) can also be set (VTP\_NPS\_TRIG\_WIDTH). This width can be used to set the desired coincidence width. If the coincidence width is desired to be set outside the VTP, it is important to use a small width for the VTP if the outside logic is edge sensisitive: the VTP trigger bit widths work in "updating" mode – that is, they will extend the pulse width if another trigger happens while the trigger output is already active. An edge-sensitive logic outside the VTP can have efficiency losses due to pileup at the VTP trigger bit.

### 9.6.4 V1495

The V1495 is a programmable logic/FPGA unit from CAEN. It is used in NPS to consolidate the trigger bits from 5 VTPs to a few trigger cables that can run to the Hall C counting room. The V1495 accepts the VTP trigger bits over 5 different ribbon cables and it outputs the trigger bits to the Hall C counting house over coaxial cable using NIM drivers. The V1495 trigger bit outputs are as follows:

V1495.F1: T1 NPS calorimeter cluster trigger (logical OR of all VTP Trigger Bit 0)

V1495.F2: T2 NPS calorimeter scintillator coincidence (npsvtp3 only, VTP Trigger Bit 1)

V1495.F3: T3 NPS calorimeter cosmic column trigger OR (logic OR of all VTP Trigger bit 2)

V1495.F4: T4 NPS calorimeter cosmic column trigger AND (logic AND of all VTP Trigger bit 2)

V1495.F5: T5 VLD (npsvtp3 only, VTP Trigger Bit 5)

V1495.F6: T6 NPS calorimeter pair trigger (logical OR of all VTP Trigger Bit 4 or multiplicity >=2 of all VTP Trigger bit 3)

V1495 triggers T1 to T5 are simple asynchronous boolean functions – no pulse width or edge detection done, so the output widths are defined by the VTP trigger pulse widths. T6 is different because the V1495 needs to perform a multiplicity trigger and reform the trigger pulse width to ensure a minimum trigger pulse width is made so that it will arrive to the counting house over the long cable run. T6 is an OR of all "Pair 2" trigger bits – these are triggers from each VTP where 2 or more clusters satisfying the pair trigger are within that crate – so the VTP will definie the V1495 pulse width for these. "Pair 1" requires a multiplicity >=2 condition (2 or more VTPs have to assert this at the same time so we trigger from 2 or more clusters in different crates). The VTP trigger pulse width defines the coincidence width used by the pair 1 multiplicity logic. When the V1495 finds 2 or more Pair 1 trigger bits asserted at the same time, it will create a 100ns pulse width on the T6 output (it works in updating mode as well, so new pairs triggers will extend this pulse width if already active).

### 9.7 Event builder data types

Data will be reported from each nps-vtp (1-5). Each VTP processes different regions of the NPS calorimeter, so the data from all VTP should be combined to see the full event information. This data will be wrapped in an EVIO formatted data bank which is not described in this document. Refer to the CODA configuration for ROC ID assignments and the readout list for the EVIO bank types/tags used to encapsulate the following described data.

### 9.7.1 Data Word Categories

Data words from the module are divided into two categories: <u>Data Type Defining</u> (bit 31 = 1) and <u>Data Type Continuation</u> (bit 31 = 0). Data Type Defining words contain a 4-bit data type tag (bits 30 - 27) along with a type dependent data payload (bits 26 - 0). Data Type Continuation words provide additional data payload (bits 30 - 0) for the *last defined data type*. Continuation words permit data payloads to span multiple words and allow for efficient packing of various data types spanning multiple data words. Any number of Data Type Continuation words may follow a Data Type Defining word.

# 9.7.2 Data Type List

- Block Header

Block Trailer

Event Header

Trigger Time

Expanded (Data SubType)

NPS Cluster

Trigger Decision

- 14 Data Not Valid (empty module)

15 Filler Word (non-data)

# Data Type: Block Header

Type: 0

Size: 1 word

Description: Indicates the beginning of a block of events. (High-speed readout of a board or a set of

boards is done in blocks of events)

| 31  | 30   | 29 | 28       | 27       | 26              | 25     | 24 |

|-----|------|----|----------|----------|-----------------|--------|----|

| 1   | 0    | 0  | 0        | 0        |                 | SLOTID |    |

| 23  | 22   | 21 | 20       | 19       | 18              | 17     | 16 |

| SLO | OTID |    | UNDE     | FINED    | EVENT_PER_BLOCK |        |    |

| 15  | 14   | 13 | 12       | 11       | 10              | 9      | 8  |

|     |      |    | EVENT_PI | ER_BLOCK |                 |        |    |

| 7   | 6    | 5  | 4        | 3        | 2               | 1      | 0  |

|     |      |    | BLOC     | K_CNT    |                 |        |    |

# BLOCK\_CNT:

Event block number (used to align blocks when building events)

# **EVENT\_PER\_BLOCK:**

Number of events in block

# **SLOTID:**

Slot ID (set by VME64x backplane)

# **Data Type: Block Trailer**

Type: 1

Size: 1 word

Description: Indicates the end of a block of events. The data words in a block are bracketed by the block header and trailer.

31 30 29 28 27 26 25 24 1 0 0 0 1 SLOTID

| 1   | 0   | 0  | 0         | 1     |    | SLOTID |    |  |

|-----|-----|----|-----------|-------|----|--------|----|--|

| 23  | 22  | 21 | 20        | 19    | 18 | 17     | 16 |  |

| SLC | TID |    | NUM_WORDS |       |    |        |    |  |

| 15  | 14  | 13 | 12        | 11    | 10 | 9      | 8  |  |

|     |     |    | NUM_V     | WORDS |    |        |    |  |

| 7   | 6   | 5  | 4         | 3     | 2  | 1      | 0  |  |

|     |     |    | NUM_V     | WORDS |    |        |    |  |

# **NUM WORDS:**

Total number of words in block of events

# **SLOTID:**

Slot ID (set by VME64x backplane)

# **Data Type: Event Header**

2

Type:

Size: 1 word

Description: Indicates the start of an event. The included trigger number is useful to ensure proper

alignment of event fragments when building events.

| 31   | 30    | 29 | 28             | 27      | 26 | 25        | 24 |

|------|-------|----|----------------|---------|----|-----------|----|

| 1    | 0     | 0  | 1              | 0       |    | UNDEFINED | )  |

| 23   | 22    | 21 | 20             | 19      | 18 | 17        | 16 |

| UNDE | FINED |    | TRIGGER_NUMBER |         |    |           |    |

| 15   | 14    | 13 | 12             | 11      | 10 | 9         | 8  |

|      |       |    | TRIGGER        | _NUMBER |    |           |    |

| 7    | 6     | 5  | 4              | 3       | 2  | 1         | 0  |

|      |       |    | TRIGGER        | _NUMBER |    |           |    |

# TRIGGER\_NUMBER:

Accepted event/trigger number

# **Data Type: Trigger Time**

Type: 3

Size: 2 words

Description:

Time of trigger occurrence relative to the most recent global reset. The time is measured by a 48bit counter that is clocked from the 250MHz system clock. The assertion of the global reset clears the counter. The de-assertion of global reset enables counter and thus sets t=0 for the module. The trigger time is necessary to ensure system synchronization and is useful in aligning event fragments when building events.

Word 1:

| 31 | 30             | 29 | 28      | 27       | 26 | 25        | 24 |  |  |

|----|----------------|----|---------|----------|----|-----------|----|--|--|

| 1  | 0              | 0  | 1       | 1        |    | UNDEFINED | )  |  |  |

| 23 | 22             | 21 | 20      | 19       | 18 | 17        | 16 |  |  |

|    | TRIGGER_TIME_L |    |         |          |    |           |    |  |  |

| 15 | 14             | 13 | 12      | 11       | 10 | 9         | 8  |  |  |

|    |                |    | TRIGGER | _TIME_ L |    |           |    |  |  |

| 7  | 6              | 5  | 4       | 3        | 2  | 1         | 0  |  |  |

|    |                |    | TRIGGER | _TIME_ L |    |           |    |  |  |

# TRIGGER\_TIME\_ L:

This is the lower 24bits of the trigger time

| XX/ | ord | ာ.   |

|-----|-----|------|

| * * | oru | . 4. |

| 31 | 30             | 29 | 28      | 27        | 26 | 25 | 24 |  |  |

|----|----------------|----|---------|-----------|----|----|----|--|--|

| 0  |                |    |         | UNDEFINED | 1  |    |    |  |  |

| 23 | 22             | 21 | 20      | 19        | 18 | 17 | 16 |  |  |

|    | TRIGGER_TIME_H |    |         |           |    |    |    |  |  |

| 15 | 14             | 13 | 12      | 11        | 10 | 9  | 8  |  |  |

|    |                |    | TRIGGER | R_TIME_ H |    |    |    |  |  |

| 7  | 6              | 5  | 4       | 3         | 2  | 1  | 0  |  |  |

|    |                |    | TRIGGER | R_TIME_ H |    |    |    |  |  |

# TRIGGER\_TIME\_ H:

This is the upper 24bits of the trigger time

**Data Type: NPS Cluster**

Type: Size: 12.11 2 words

This data type identifies a cluster Description:

Word 1:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|----|----|----|----|----|----|----|----|

| 1  | 1  | 1  | 0  | 0  | 1  | 0  | 1  |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 1  | -  | -  | =  | -  | -  | ı  | =  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

| -  | -  |    |    |    | Е  |    |    |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    |    |    | E  |    |    |    |    |

### E: 14bit unsigned cluster energy

| Word 2: |    |    |    |    |    |    |    |

|---------|----|----|----|----|----|----|----|

| 31      | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

| 0       | -  | -  | -  | -  | -  | Ŋ  | Y  |

| 23      | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|         | Y  |    |    |    | X  |    |    |

| 15      | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

| X       |    | ľ  | V  |    |    | T  |    |

| 7       | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|         |    |    | T  |    |    |    |    |

**X**:

Y:

5bit unsigned cluster X coordinate 6bit unsigned cluster Y coordinate 11bit cluster time in 4ns units referenced from the beginning of the readout window T:

N: 4bit number of hits in the cluster

# **Data Type: Trigger Decision**

Type: 13 Size: 2 words

Description: This data type reports trigger decision made. A 32bit trigger bit pattern is reported with

4ns timestamp relative to the readout window indicates where the VTP found a valid trigger. If multiple triggers happen at the same time then multiple bits will be set in the 32bit trigger bit pattern word. A trigger decision pattern will be recorded for each unique

time in the VTP readout window.

| *** 1 | -   |   |

|-------|-----|---|

| Word  | - 1 | ٠ |

| w ora | - 1 |   |

|       |     |   |

| 31 | 30 | 29 | 28    | 27      | 26 | 25 | 24 |  |  |

|----|----|----|-------|---------|----|----|----|--|--|

| 1  | 1  | 1  | 0     | 1       |    | T  |    |  |  |

| 23 | 22 | 21 | 20    | 19      | 18 | 17 | 16 |  |  |

|    | Т  |    |       |         |    |    |    |  |  |

| 15 | 14 | 13 | 12    | 11      | 10 | 9  | 8  |  |  |

|    |    |    | TRIGE | BITS_L  |    |    |    |  |  |

| 7  | 6  | 5  | 4     | 3       | 2  | 1  | 0  |  |  |

|    |    |    | TRIGB | SITS _L |    |    |    |  |  |

# TRIGBITS\_L: Trigger bits 15:0

T: 11bit trigger bit pattern time in 4ns units

(referenced from the beginning of the readout window)

| W | Λt | Ы | 2. |  |

|---|----|---|----|--|

|   |    |   |    |  |

| 31         | 30 | 29 | 28    | 27     | 26 | 25 | 24 |

|------------|----|----|-------|--------|----|----|----|

| 0          | -  | -  | -     | -      | -  | -  | -  |

| 23         | 22 | 21 | 20    | 19     | 18 | 17 | 16 |

| -          | -  | -  | -     | -      | -  | -  | -  |

| 15         | 14 | 13 | 12    | 11     | 10 | 9  | 8  |

|            |    |    | TRIGE | BITS_H |    |    |    |

| 7          | 6  | 5  | 4     | 3      | 2  | 1  | 0  |

| TRIGBITS_H |    |    |       |        |    |    |    |

# TRIGBITS\_H: Trigger bits 31:16

Note: For NPS, the following trigger bits have been defined:

**TriggerBit0:** NPS Cluster Trigger, cluster >= threshold

**TriggerBit1:** Cosmic scintillator trigger, or(ScintTop) and or(ScintBot)

**TriggerBit2:** Cosmic calorimeter column trigger, or(mult(Column<sub>n</sub>) > mult\_min)

These trigger bits from each nps-vtp will be processed in an additional stage using a CAEN

V1495 FPGA module so the mapping of these bits into the Trigger Supervisor will be different from above (this should be documented in the NPS DAQ trigger setup when implemented).

Data Type: Data Not Valid

Type: 14 Size: 1 word Description: Module has no data available for readout. This can if the module is being read out too quickly after receiving (event building is in process and no data words have been put into the buffer yet) a trigger or if the module doesn't have any events to report.

| 31 | 30        | 29 | 28 | 27 | 26        | 25 | 24 |  |

|----|-----------|----|----|----|-----------|----|----|--|

| 1  | 1         | 1  | 1  | 0  | UNDEFINED |    |    |  |

| 23 | 22        | 21 | 20 | 19 | 18        | 17 | 16 |  |

|    | UNDEFINED |    |    |    |           |    |    |  |

| 15 | 14        | 13 | 12 | 11 | 10        | 9  | 8  |  |

|    | UNDEFINED |    |    |    |           |    |    |  |

| 7  | 6         | 5  | 4  | 3  | 2         | 1  | 0  |  |

|    | UNDEFINED |    |    |    |           |    |    |  |

# Data Type: Filler Word

Type: 15 Size: 1 word

Description: Non-data word appended to the block of events. This is used to force the total number of

32-bit words read out of a module to be a multiple of 2 or 4 when

| 32 of words read out of a module to be a maniple of 2 of which |    |    |    |    |           |    |    |

|----------------------------------------------------------------|----|----|----|----|-----------|----|----|

| 31                                                             | 30 | 29 | 28 | 27 | 26        | 25 | 24 |

| 1                                                              | 1  | 1  | 1  | 1  | UNDEFINED |    |    |

| 23                                                             | 22 | 21 | 20 | 19 | 18        | 17 | 16 |

| UNDEFINED                                                      |    |    |    |    |           |    |    |

| 15                                                             | 14 | 13 | 12 | 11 | 10        | 9  | 8  |

| UNDEFINED                                                      |    |    |    |    |           |    |    |

| 7                                                              | 6  | 5  | 4  | 3  | 2         | 1  | 0  |

| UNDEFINED                                                      |    |    |    |    |           |    |    |

# 9.8 Configuration Parameters

### VTP W WIDTH < width>

Sets the VTP readout window width in units of nanosecond ranging from 0 to 8188. VTP triggers and clusters in the readout window will be recorded for each VTP event.

# VTP\_W\_OFFSET <offset>

Sets the VTP readout window offset (or lookback time) in units of nanosecond ranging from 0 to 8191. VTP triggers and clusters in the readout window will be recorded for each VTP event. Note this window parameter is also used by the sparisfication cluster detection logic (the sparsification offset is relative to this window offset).

<en1> to <en16> can be 0 or 1. 0 indicates the VXS payload card is disabled, 1 indicates the VXS payload card is enabled. These payloads are the FADC payload trigger enable/disable flags and must be setup according to the used FADC slots used in the trigger. The following table shows the map of the payload number to VME slot:

| VXS Payload | VME Slot |

|-------------|----------|

| 1           | 10       |

| 2           | 13       |

| 3           | 9        |

| 4           | 14       |

| 5           | 8        |

| 6           | 15       |

| 7           | 7        |

| 8           | 16       |

| 9           | 6        |

| 10          | 17       |

| 11          | 5        |

| 12          | 18       |

| 13          | 4        |

| 14          | 19       |

| 15          | 4        |

| 16          | 20       |

# **VTP\_FIBER\_EN** <en0> <en1> <en2> <en3>

<en0> to <en3> can be 0 or 1.0 indicates the fiber is disabled, 1 indicates the fiber is enabled. These parameters are set to ensure fibers between the nps-vtp crates are enabled to share border FADC hits so clustering at crate perimeters works and also to share found cluster information so that sparsification channel patterns work. The following table illustrates the used fiber ports:

| VTP Optical Connection Table |    |          |        |  |  |

|------------------------------|----|----------|--------|--|--|

|                              |    |          |        |  |  |

|                              | m: | To:      |        |  |  |

| nps-vtp#                     | T# | nps-vtp# | T#     |  |  |

| 5                            | 4  | unused   | unused |  |  |

| 5                            | 3  | 4        | 4      |  |  |

| 5                            | 2  | unused   | unused |  |  |

| 5                            | 1  | 4        | 2      |  |  |

| 4                            | 4  | 5        | 3      |  |  |

| 4                            | 3  | 3        | 4      |  |  |

| 4                            | 2  | 5        | 1      |  |  |

| 4                            | 1  | 3        | 2      |  |  |

| 3                            | 4  | 4        | 3      |  |  |

| 3                            | 3  | 2        | 4      |  |  |

| 3                            | 2  | 4        | 1      |  |  |

| 3                            | 1  | 2        | 2      |  |  |

| 2                            | 4  | 3        | 3      |  |  |

| 2                            | 3  | 1        | 4      |  |  |

| 2                            | 2  | 3        | 1      |  |  |

| 2                            | 1  | 1        | 2      |  |  |

| 1                            | 4  | 2        | 3      |  |  |

| 1                            | 3  | unused   | unused |  |  |

| 1                            | 2  | 2        | 1      |  |  |

| 1                            | 1  | unused   | unused |  |  |

# VTP\_NPS\_COSMIC\_SCINT\_DT <dt>

<dt> is the scintillator hit coincidence time. Valid values for <dt> range from 0 to 7 and units are in 4ns.

# VTP\_NPS\_COSMIC\_COLUMN\_MULTMIN <mult>

<mult> is the minimum multiplicity of blocks in a single crate and calorimeter column to have a hit to create a cosmic column trigger for that crate. Valid values for <mult> range from 1 to 8.

# VTP\_NPS\_COSMIC\_COLUMN\_DT <dt>

<dt> is the column hit coincidence time. Valid values for <dt> range from 0 to 7 and units are in 4ns.

# VTP\_NPS\_COSMIC\_COLUMN\_VETO\_EN <en>

<en> disables (when 0) the cosmic column veto logic, and enables it when 1. Enabling this veto will reject cosmic column triggers when there are hits in more than 1 column within a single crate.

# VTP\_NPS\_ECALCLUSTER\_CRATE\_ID <id>

<id> must be set to a value of 1 to 5, matching the number in the VTP host name (the # in: nps-vtp#). This will ensure clusters are recorded with the correct Y offset in the event data.

### VTP\_NPS\_ECALCLUSTER\_HIT\_DT <dt>

<dt> is the cluster hit coincidence time with respect to seed hit. Valid values for <dt> range from 0 to 7 and units are in +/-4ns (e.g. dt=0 means 0ns coincidence, dt=1 means +/-4ns coincidence, etc...)

### VTP NPS ECALCLUSTER SEED THR <thr>

<thr> is the clustering minimum seed threshold – a channel must have a hit with this energy or greater to initiate finding a cluster. Valid values for <thr> range from 0 to 16383. The units are arbitrary and depend on the FADC250 channel gain conversions, which nominally target 1MeV units for this threshold.

# VTP\_NPS\_ECALCLUSTER\_NHIT\_MIN <min>

<min> is the minimum number of hits a cluster must have in order to be accepted (for cluster singles, pair, and readout). Valid values for <min> range from 1 to 9.

# VTP\_NPS\_ECALCLUSTER\_CLUSTER\_TRIGGER\_THR <thr>

<thr> is the clustering minimum cluster energy threshold to create a singles cluster trigger. Valid values for <thr> range from 0 to 16383. The units are arbitrary and depend on the FADC250 channel gain conversions, which nominally target 1MeV units for this threshold.

### VTP\_NPS\_ECALCLUSTER\_CLUSTER\_READOUT\_THR <thr>

<thr> is the clustering minimum cluster energy threshold for sparsified readout to readout FADC channels around clusters. Valid values for <thr> range from 0 to 16383. The units are arbitrary and depend on the FADC250 channel gain conversions, which nominally target 1MeV units for this threshold.

### VTP\_NPS\_ECALCLUSTER\_CLUSTER\_PAIR\_TRIGGER\_THR <thr>

<thr> is the clustering minimum cluster energy threshold to create a pair1 or pair2 trigger (this threshold applies to individual clusters in the pair). Valid values for <thr> range from 0 to 16383. The units are arbitrary and depend on the FADC250 channel gain conversions, which nominally target 1MeV units for this threshold.

# VTP\_NPS\_ECALCLUSTER\_CLUSTER\_PAIR\_TRIGGER\_WIDTH < width>

<width> is the cluster pair time coincidence window that is used for the cluster pair trigger for cluster found in the same crate. Valid values range from 0 to 124 and units are in 1ns.

### VTP NPS FADCMASK MODE < mode>

When <mode>=0 the sparsification logic reads out 5x5 FADC channel patterns. When <mode>=1 the sparsification logic reads out 7x7 FADC channel patterns.

# VTP\_NPS\_FADCMASK\_PRESCALE

This prescale value can be set to occasionally readout all channels when sparisification mode is enabled. It provides a way to have a small fraction of events having all waveforms for potentially useful/special analysis that sparisfication mode may complicate. When cprescale> is 0, sparsification is disabled and all events have all FADC channels readout. When cprescale> is between 1 and 65534, every cprescale>+1 event will have all FADC channels readout. When cprescale> = 65535 then sparsification is enabled for all events.

# VTP NPS FADCMASK WIDTH <width>

Sparsification cluster hit <width> that defines how long clusters persist in sparisification detection logic once found. Valid range is 0 to 8188 and units are in nanoseconds. This width is the time the sparsification logic looks before and up to the the VTP\_NPS\_FADCMASK\_OFFSET point in the readout window.

# VTP\_NPS\_FADCMASK\_OFFSET <offset>

Sparsification cluster hit <offset> that defines the time the sparisification detection logic once looks in the VTP readout window for clusters to determine FADC readout masks. Valid range is 0 to 8188 and units are in nanoseconds. The parameter is relative to the VTP\_W\_OFFSET parameter: this is intentional to simplify the timing - looking at the VTP cluster event data the time of cluster in the window

# VTP\_NPS\_TRIG\_DELAY < trgbit> < delay>

<trgbit> selects the trigger bit number, 0 to 31 that the <delay> will apply to. <delay> is the amount of delay to add to the trigger bit in nanoseconds. Valid values are 0 to 1020.

# VTP\_NPS\_TRIG\_PRESCALE < trgbit> < prescale>

<trgbit> selects the trigger bit number, 0 to 31 that the prescale> will apply to. prescale> is the amount to prescale the trigger bit outputs. 0 will disable the trigger bit output. 1 will enable the trigger bit output with no prescale. Values 2 to 65535 will prescale the output by that amount (e.g. prescale>=2 will pulse the trigger output every other trigger...

# VTP\_NPS\_TRIG\_LATENCY < latency>

<latency> is the VTP trigger latency in nanosecond units (this is roughly the amount of time from when a signal goes into the FADC to when the VTP will generate a trigger puse for cosmic, clusters, VLD, etc).

Valid range is 0 to 8188, but some settings dictate the minimum acceptable value: for NPS it is around 2300ns minimum required for this parameter).

### VTP NPS TRIG WIDTH < width>

<width> is the VTP trigger output pulse width generated each time a trigger condition is satisfied. Units are in nanosecond. Valid range is 0 to 1020, actual pulse width will be this value +4ns.

### 9.9 Latencies

Some notes on general latencies expected through the trigger system:

A->B: ~400ns (FADC pulse to VTP Serdes RX output)

A->B->C: ~1700ns (FADC pulse to VTP from adjacent crate, to VTP over fiber Serdes RX)

A->B->C->D: ~2300ns (FADC pulse to VTP trigger output)

A->B->C->D: ~2330ns (FADC pulse to V1495 trigger output)

Most delays in the trigger processing is moving data around over serial links (VXS backplanes and fibers). A small amount is needed by the FADC to perform the "NSA" section of the pulse integration (time is roughly the amount of time defined by the NSA integration parameter). THe VTP clustering takes no more than a few hundred nanoseconds. The resulting latency ~2300ns requires the parameter VTP\_NPS\_TRIG\_LATENCY be at least a little larger to ensure the trigger operates with a fixed latency.

### 9.10 Verification

The NPS trigger was verified through few ways, mainly: (1) FPGA logic simulator and (2) C/C++ logic emulator comparing VTP event builder data to reconstructed FADC data.

### (1) FPGA logic simulation

This simulation compiles and simulates the FPGA code for the TI, FADC250, VTP, and V1495 modules that are all used in the real setup. The simulation runs the full system (5 crates, 1080 FADC channels) and consists of walking FADC hits across all possible cluster positions to ensure 3x3 clustering tests the FADC to calorimeter map and cluster across crate perimeters work. The simulation reads out the FADC event data and also the VTP event data to cross checking between them can be done. This includes testing of the sparisifcation logic mode to ensure FADC channels that don't paricipate in a cluster are not read while FADC channels that are near clusters over cluster readout thresholds are readout.

This simulator is extremely slow, taking about 1 hour of runtime to configure (a lot of VME emulation accesses to setup the FADCs and VTPs) and start to issue triggers. Once configuration is complete triggers and event readout can run at around 1 readout event every few minutes. Usually smaller scales of the setup were used to debug in much shorter time frames, then overnight simulation where run to check the full setup. This simulator is very accurate and very often reproduces problems found in real setups making it extremely valuable. It can also read EVIO files from CODA to process events to check the trigger logic on them.

The simulation software is Aldec Riviera and simulates using VHDL, Verilog, C, and C++ source codes.

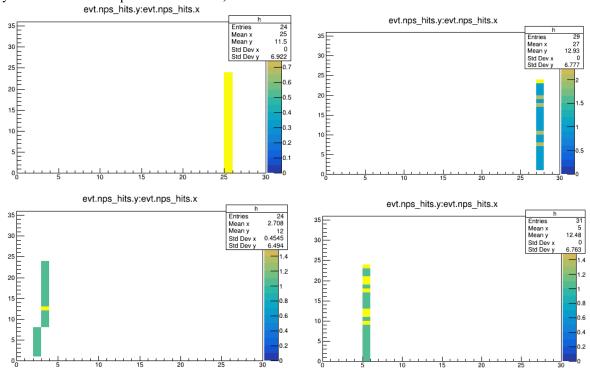

# (2) C/C++ Logic Emulator

This is simple C/C++ application that emulates the trigger logic. It reads EVIO files and processes the FADC data to reconstruct the trigger logic. It also reads the VTP event data which has the trigger logic responses (trigger bits, times, and clusters). FADC reconstructed plots and be compared against the VTP plots directly as well as the cluster and trigger bits for all individual events. The accuracy is extremely good

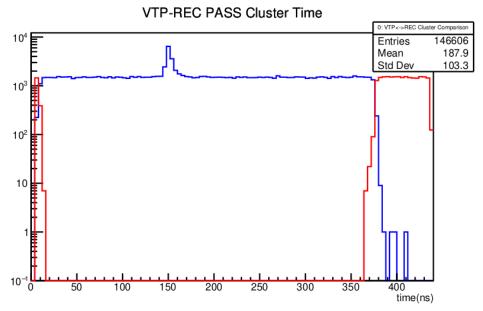

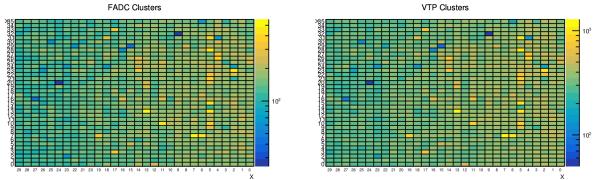

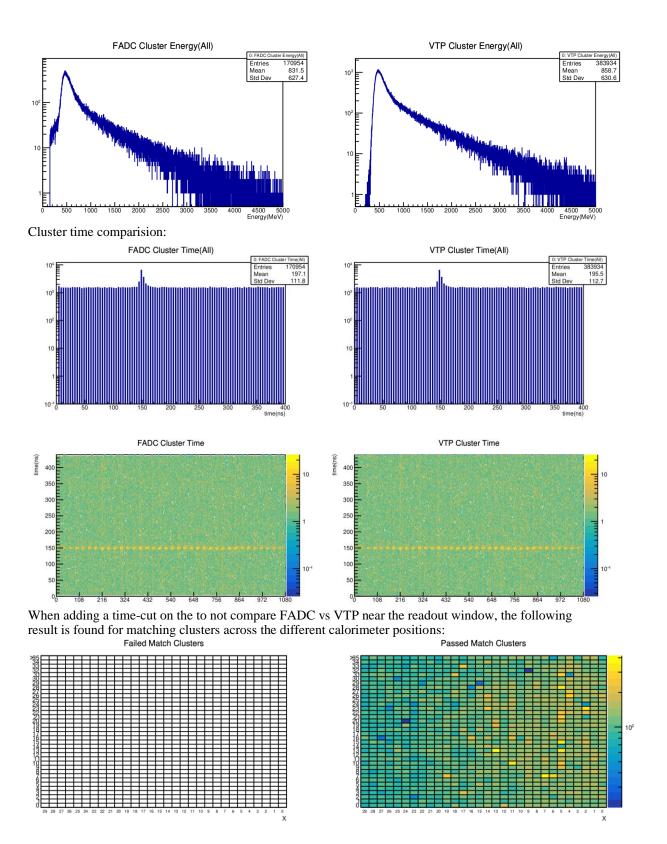

as shown here where all FADC reconstructed trigger clusters are compared to the VTP reported clusters as a function of time in the readout window: